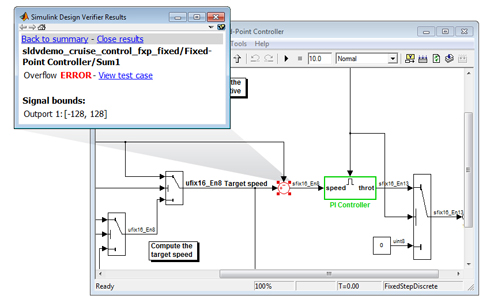

Polyspace解析技術を搭載した「Simulink Design Verifier 2.0」を発表、MathWorks:Simulinkモデルで自動エラー検出を可能に

MathWorksは、Simulinkモデルで自動エラー検出を可能にするため、「Simulink Design Verifier」にPolyspace解析技術を搭載した「Simulink Design Verifier 2.0」を開発し、提供を開始する。

» 2011年07月08日 12時57分 公開

[八木沢篤,@IT MONOist]

MathWorksは2011年7月7日(米国時間)、Simulinkモデルで自動エラー検出を可能にするため、「Simulink Design Verifier」にPolyspace解析技術を搭載した「Simulink Design Verifier 2.0」を開発し、提供を開始すること(価格は120万円~)を発表した。

同製品では、Polyspaceエラー検出機能が既存のプロパティ検証やテスト生成機能と統合されるため、設計エラーの根本的原因の発見や修正にかかる時間を短縮できる上、検証と妥当性確認にかかる全体的なコストの削減を可能にするという。

航空宇宙、自動車、医療、産業オートメーション、および産業機械の各分野において、同製品が提供する形式的解析手法を使用し、モデルベースデザインを適用することで、詳細なテストやシミュレーションを行わなくても、SimulinkモデルやStateflowモデルの設計上の欠陥を特定できるようになるとしている。

以下に、同製品の特長を示す。

- デッドロジック、整数や固定小数点のオーバーフロー、ゼロ除算、アサーション違反などを検出

- 機能的な要求仕様やセキュリティに関する要求仕様をモデリングするためのブロックや関数

- 機能的な要求仕様とモデルカバレッジの目標から、ベクトル生成をテスト

- 解析とデバッグのために違反の例を生成し、プロパティを検証

- 固定小数点と浮動小数点のモデルをサポート

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -- EDA�ス�ス�ス�ス鬨セ雜」�ス�ッ髯晢ソス隰碁�托スー蟷�コ�ス�ス�ス�ス�ス�ィ�ス�ス�ス�ュ鬯ョ�ォ�ス�ェ鬯ゥ蟷「�ソ�ス�ス�ソ�ス�ス鬮ッ�キ隶手エ具スセ蟷�答�ス�ァ�ス�ス�ス�ス髯晢スイ�ス�ィ驛「譎「�ス�、鬩幢ス「隴趣ス「�ス�ス�ス�シ鬩幢ス「隴趣ス「�ス�ス�ス�ォ鬩搾スオ�ス�コ�ス�ス�ス�ッ鬩搾スオ�ス�コ�ス�ス�ス�ゥ鬩搾スオ�ス�コ�ス�ス�ス�ス驕カ蜑ー縺費ソス�ク�ス�コ�ス�ス�ス�カ�ス�ス�ス�ス髮具ソス�シ蜿ッツ�ス縺、ツ鬩幢ス「隴趣ス「�ス�ソ�ス�ス驍オ�コ陋滂ス。�ス�ケ�ス�ァ�ス�ス�ス�、鬩幢ス「隴趣ス「�ス�ス�ス�ウ鬩幢ス「�ス�ァ髯キ�サ髣鯉スィ�ス�ソ�ス�ス鬮ッ�キ騾包スサ�ス�コ陋滂スェ�ス�ス鬮ッ譎「�ソ�ス�ス�シ�ス�ア�ス�ス�ス�・鬩搾スオ�ス�コ髮具ソス竏橸ソス�ス遶擾スォ�ス�ク�ス�コ�ス�ス�ス�ョ鬯ゥ遨ゑスシ諷環�ス�ゥ�ス�ス�ス�ィ�ス�ス�ス�」

- FPGA鬯ョ�ォ�ス�ェ�ス�ス�ス�ュ鬯ョ�ォ�ス�ェ髯具スケ�ス�サ驕カ莨∬アェ�ス�ク�ス�コ鬩怜遜�ス�ォ�ス�ス�ス�ス鬩幢ス「�ス�ァ鬮ォ�ェ驕ス�ュT4鬩搾スオ�ス�コ�ス�ス�ス�ィLUT6鬩搾スオ�ス�イ驕カ謫セ�ス�オ�ス�ス�ス�ッ鬩募争豎夲ソス�ス�ス�シ�ス�ス�ス�ス�ス�ス�ス�オ髯キ莠・豐コ�ス�」�ス�。鬩搾スオ�ス�コ�ス�ス�ス�ォ鬯ョ�ォ驕ィ繧托スス�ケ隴趣ス「�ス�ス驍�私�ス�ォ�ス�、�ス�ス�ス�ァ鬯ョ�「�ス�ュ�ス�ス�ス�ス鬩搾スオ�ス�コ�ス�ス�ス�ョ鬯ッ�ゥ隰悟・�スス�シ髮具スサ�ス�シ�ス�ス

- 鬩幢ス「隴乗��ス�ク陞ゑソス�ス�ソ�ス�ス鬩幢ス「隴取得�ス�ウ�ス�ィ驍オ�コ髢ァ�イ�ス�ケ�ス�ァ�ス�ス�ス�ァ鬩幢ス「�ス�ァ�ス�ス�ス�「鬯ョ�ォ�ス�ェ�ス�ス�ス�ュ鬯ョ�ォ�ス�ェ髯具スケ�ス�サ驕カ鬆托ス・�「隲、謫セ�ソ�ス�ス�ケ鬯ゥ謳セ�ソ�ス�ス�ソ�ス�ス驕カ髮�スョ螟イ�ス�ュ雋�スス�ス�「隰�∞�ス�ス�ス�サ髮矩。疲捗�つ�ス�ス�ス�ァ鬩幢ス「�ス�ァ髯句ケ「�ス�オ�ス�ス郢ァ莨夲スス�ク�ス�コ髮具ソス竏橸ソス�ス髢セ�・�ス�ク�ス�コ髯キ�キ�ス�カ�ス縺、ツ驕カ荳橸ス」�ケ�ス�スホ費ソス�ァ�ス�ス�ス�ケ鬩幢ス「隴惹シ夲スス�」�ス�ッ驛、�ス�ス�セ鬯ョ�ォ隰碁�代≦PGA鬯ョ�ッ�ス�ャ�ス�ス�ス�ス鬮ッ�キ�ス�ゥ驕カ謫セ�ス�ォ�ス�ス�ス�セ�ス�ス�ス�、鬩搾スオ�ス�コ�ス�ス�ス�ィ鬩搾スオ�ス�コ�ス�ス�ス�ッ�ス�ス�ス�ス�ス�ス�ス�ス

- [MONOist鬯ゥ謳セ�ス�ア�ス�ス�ス�ィ鬯ッ�ョ�ス�ョ�ス�ス�ス�ス�ス荳サ閼ケ 鬯ゥ謳セ�ス�ィ�ス�ス�ス�ス驕カ謫セ�ス�ゥ鬯ョ�エ髮懶ス」�ス�ス�ス�シ鬩搾スオ�ス�コ�ス�ス�ス�ソ鬮ォ�カ陋ケ�ス�ス�コ�ス�キ髯キ謳セ�ス�」鬮ッ�キ�ス�キ髣比シ夲スス�」�ス�ス�ス�ス鬩幢ス「�ス�ァ�ス�ス�ス�オ鬩幢ス「�ス�ァ�ス�ス�ス�、鬩幢ス「隴趣ソス�ソ�ス�ス�ス�ス�ス鬩幢ス「�ス�ァ�ス�ス�ス�サ鬩幢ス「�ス�ァ�ス�ス�ス�ュ鬩幢ス「隴趣ス「�ス�ス�ス�・鬩幢ス「隴趣ス「�ス�ス�ス�ェ鬩幢ス「隴趣ス「�ス�ソ�ス�ス驍オ�コ�ス�ス雎取ゥク�ソ�ス�ス�セ鬯ゥ蛹�スス�イ髫ー雋サ�ス�カ�ス�ス�ス�ス鬮ッ�キ隶手エ具スセ蟷�スャ�ョ�ス�ス陜ョ�。�ス�ス�ス�ソ鬮ォ�エ雋翫q�ス�ス�ス�サ

- [MONOist鬯ゥ謳セ�ス�ア�ス�ス�ス�ィ鬯ッ�ョ�ス�ョ�ス�ス�ス�ス�ス荳サ閼ケ 鬩幢ス「隴趣ス「�ス�ス�ス�ェ鬩幢ス「�ス�ァ�ス�ス�ス�「鬩幢ス「隴趣ス「�ス�ス�ス�ォ鬩幢ス「�ス�ァ�ス�ス�ス�ソ鬩幢ス「�ス�ァ�ス�ス�ス�、鬩幢ス「隴趣ス「�ス�ソ�ス�スOS鬮ッ蜈キ�ス�サ髯滓誓�ス�コ�ス�ス�ス�シ髫エ謫セ�ス�エ驕カ謫セ�ス�ェ鬩搾スオ�ス�コ�ス�ス�ス�ィ鬩幢ス「�ス�ァ�ス�ス�ス�ス�ス�ス�ス�シ鬮「�ァ�ス�イ�ス�ス�ス�ャ�ス�ス�ス�ャ31鬮ッ諛�サク�ス�ゥ�ス�ク�ス�ス�ス�ス�ス�ス�ス�ス35鬮ッ諛�サク�ス�ゥ�ス�ク�ス�ス�ス�シ�ス�ス�ス�ス

Special Contents 1

- PR -Special Contents 2

- PR -Special Site

- PR -Pickup Contents

- PR -鬩幢ス「�ス�ァ�ス�ス�ス�ウ鬩幢ス「隴趣ス「�ス�ス�ス�シ鬩幢ス「隴惹シ夲スス�ソ�ス�ォ�ス�ス�ス�ス鬩幢ス「隴趣ス「�ス�ス�ス�ェ鬩幢ス「隴趣ス「�ス�ス�ス�ウ鬩幢ス「�ス�ァ�ス�ス�ス�ッ

組み込み開発の記事ランキング

- ブレッドボードの表裏を使ってFPGA評価ボードの万能UI「dpad」を新生させる

- 産総研の最新スパコン「ABCI 3.0」が生成AIの研究開発と社会実装を加速する

- 米中が先行する汎用ロボット、日本がロボット大国に返り咲くには何が必要なのか

- 車載マイコンで快走のインフィニオン、なぜRISC-Vを採用するのか

- 大阪・関西万博の体験型パビリオンは競争率が高過ぎてビビる

- インフィニオンの機械学習向けマイコンが「NVIDIA TAO」をサポート

- LTE不感エリアでWi-Fi HaLowを活用したドローン実験を実施

- CAN通信におけるデータ送信の仕組みとは?

- 45万人だけが参加できる万博のパナソニックパビリオン、半年かけた実証実験も

- CANプロトコルを理解するための基礎知識

画像1 「Simulink Design Verifier 2.0」の画面イメージ

画像1 「Simulink Design Verifier 2.0」の画面イメージ いまさら聞けない モデルベース開発入門

いまさら聞けない モデルベース開発入門 トヨタとデンソー、量産開発に適用しているMATLABのバージョンを「R2010b」へ移行

トヨタとデンソー、量産開発に適用しているMATLABのバージョンを「R2010b」へ移行