進化する開発環境が一堂に――設計開発者の羅針盤「EDS Fair 2012」:EDS Fair 2012(1/2 ページ)

設計ソリューションの必須技術を網羅する展示会「EDS Fair 2012」がパシフィコ横浜で開催。「バーチャル・プロトタイプ」や「ESL」など最新の開発環境が紹介された。

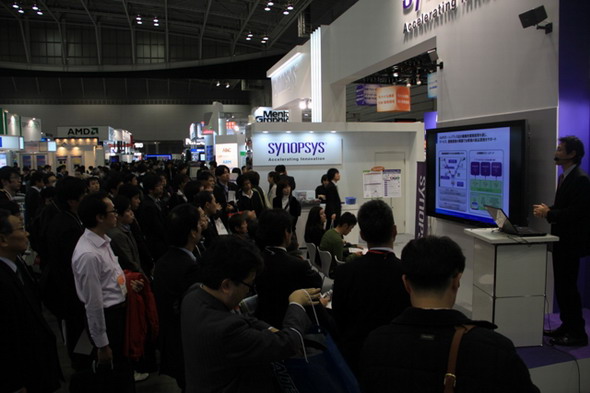

EDS Fair 2012(Electronic Design and Solution Fair 2012)が2012年11月14〜16日の3日間、横浜・みなとみらいのパシフィコ横浜で開催された。同イベントは「Software to Siliconの大海へ」乗り出す開発者に対して、「海図と羅針盤」となる開発環境を提供していくことが大きな目的となっている。会場では「バーチャル・プロトタイプ」や「ESL」などをキーワードにした最新の開発環境が示された。

仮想環境で製品開発の期間を短縮

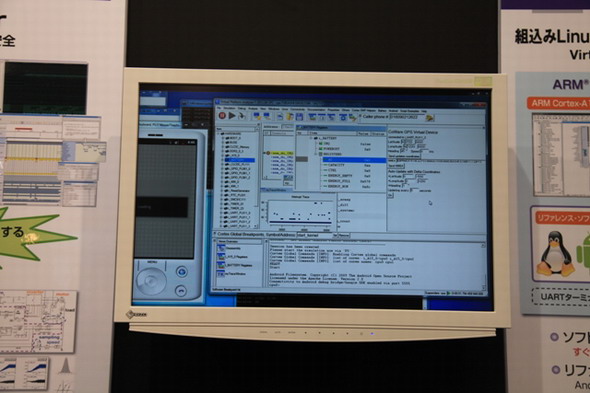

日本シノプシスは、半導体の設計および製造に用いられるさまざまなEDAツールを統合して提供する。その中でも、バーチャル・プロトタイピング・ソリューション「Virtualizer」(画像1)などが来場者の注目を集めていた。

バーチャル・プロトタイプは、開発対象のシステムをソフトウェア・モデルで表現したもの。このモデルを事前に準備することで、ハードウェア(実機)が完成する前から、ソフトウェアの開発・検証を行うことができる。最終的にシステムの開発期間を大幅に短縮することができる。

「Virtualizerは、既に国内でも複数の自動車メーカーやモバイル端末メーカーに導入され、モータ制御など複雑な電子回路設計を効率よく開発するために活用されている」(説明員)という。そして、「ARMやMIPS、PowerPC、SH、V850、Tensilicaといった主要なプロセッサ・アーキテクチャや、PCI Expressに代表される各種インタフェースIPなどのモデル・ライブラリを豊富に用意しているのが当社の強みの1つ」と続けた。

車載機器やモバイル端末などに搭載される電子回路は、高速処理と低消費電力を両立させるため、プロセッサのメニコア化やハードウェアによる並列処理方式への移行が進む。こうした動きに伴って、ハードウェアの検証やソフトウェアの開発が複雑化し、設計者にかかる負荷は急激に増えている。最新の電子回路設計を、ハードウェアとソフトウェアを独立して開発していた旧来の開発手法で行った場合、設計期間は8〜20カ月も増加する。バーチャル・プロトタイプの開発手法を導入すると、旧来方式に比べて開発期間は最大で6カ月短縮できる、との試算もある。

Virtualizerの最新バージョンでは、モデル・オーサリング機能の強化などを行った。これにより、システムレベル・モデルの作成時間をこれまでより3倍速くすることができるという。

日本シノプシスは、バーチャル・プロトタイプとFPGAベース・ハードウェア・プロトタイプを統合した「ハイブリッド・プロトタイピング・ソリューション」も会場で提案した。ソフトウェア・モデルの一部をFPGA上に実装することで、より実機に近い実行スピードでソフトウェアを検証することが可能となる。今回は、FPGAベース・ハードウェア・プロトタイピング・ソリューションの新製品「HAPS-70」(写真2)を展示した。この、プロトタイピング・システムにはザイリンクスの最新FPGA「Virtex-7」が搭載されており、最大1億4400万ゲートまで実装することが可能となっている。システム性能も従来品に比べて最大3倍向上させた。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 品質保証とは何か、その定義を改めて考える

- タイの半導体製造工場で新棟が完成、ソニーセミコンが生産力を強化

- 三菱重工が航空機エンジン部品工場を増強、内製力強化で完全一貫生産を実現

- パワー半導体の電流測定が正確に、光プローブを用いた電流波形測定用センサー

- ルネサスが甲府工場で300mmウエハーライン稼働、パワー半導体の生産能力を2倍に

- 日立産機が三菱電機 名古屋製作所の配電用変圧器事業を譲受、2026年4月に統合完了

- 工場でCO2排出量1次情報をなぜ取得すべきなのか 85%以上の削減効果も

- 誤差9割、コストを抑えるためにもCO2排出量は測った方がよい

- OTセキュリティを巡るエネルギー業界の法改正とは、変わる事業者の事故対応

- IEC 62443とは何か、工場のサイバーセキュリティ対策のカギを握る国際標準を解説

横浜・みなとみらいのパシフィコ横浜で開催された「EDS Fair 2012」

横浜・みなとみらいのパシフィコ横浜で開催された「EDS Fair 2012」 画像1 Virtualizerの設定画面

画像1 Virtualizerの設定画面 画像2 最新FPGA搭載されており、最大1億4400万ゲートまで実装することが可能となったFPGAベース・ハードウェア・プロトタイピング・ソリューション

画像2 最新FPGA搭載されており、最大1億4400万ゲートまで実装することが可能となったFPGAベース・ハードウェア・プロトタイピング・ソリューション