第7回 銅の限界:前田真一の最新実装技術あれこれ塾(1/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第7回は、現在も広く利用されている、銅を用いた電気インタフェースの高速化の限界について考察します。

本連載は「エレクトロニクス実装技術」2011年10月号の記事を転載しています。

1. 銅配線での高速信号伝送

光と銅について、もう一度、銅の限界について考えてみます。

2000年頃はPCIバスが66MHzの時代で伝送線路の損失は考慮していませんでした。損失の影響が現れる数百MHz以上の高速化には多くの問題があると考えられていました。このため、その頃は1GHzの壁といわれていました。高速信号は銅箔による伝送線路では損失が問題となり、光が必要だろうといわれていました。

これからは光の時代といわれ、通信回線の光ケーブル化が急がれると同時に、基板配線をどうして光伝送にするかが考えられはじめました。

しかし、バスを並列データ転送方式から直列データ転送方式にすることにより、銅箔によるGHz信号の伝送の可能性が検討と高速シリアルバスの提案がされはじめました。

2002年にこれらの規格の一つ、1.25GHzのPCI Expressが発表され、銅箔によるGHzの壁をあっさり突破してしまいました。

しかし、1GHzの壁を破るためには、このPCI Expressでは、基板の配線に関して、これまでにはない多くの技術と規約を設けました。

規格については、基板の規格を配線のインピーダンス制御、配線の引き回し、参考的な基板の層構成までを規格の中に定義しました(図1)。

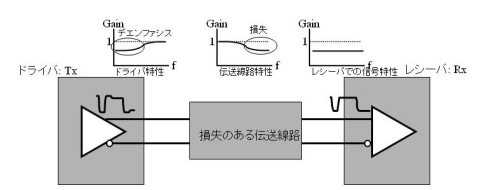

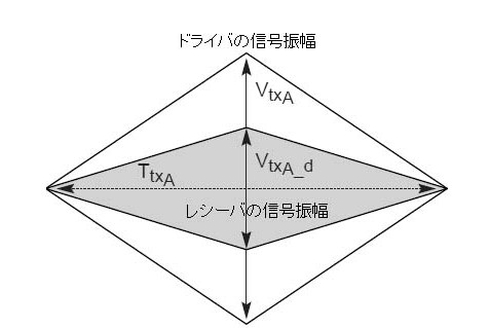

また、この信号速度では、損失が大きな問題となるため、ドライバからレシーバまでの配線損失量も規格として定義しました(図2)。

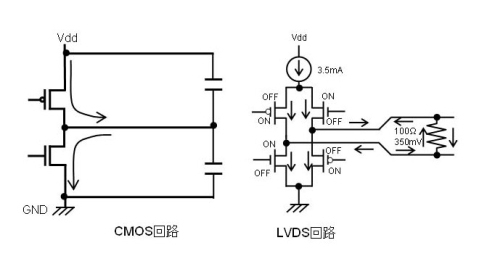

高速伝送のため、これまでのPCIバスに使われていたCMOSロジック回路を新しい差動電流ドライバであるLVDS(Low Voltage Differential Signaling)へと変更しました(図3)。

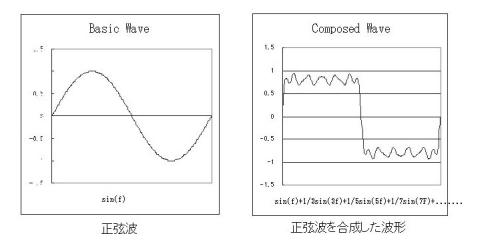

デジタル信号は基本となるデータ転送速度の正弦波を基本として、基本正弦波のn倍の周波数の正弦波がたくさん合成された方形波が基本となっています(図4)。損失は信号の周波数に比例するので、高い周波数の成分ほど損失が大きくなります。

方形波の高い周波数成分は信号の高い立ち上がり、立ち下り成分を作っているので、損失が大きくなると、方形波はだんだん立ち上がり、立ち下りが遅くなってきて、ついには正弦波に近い波形になってしまいます(図5)。

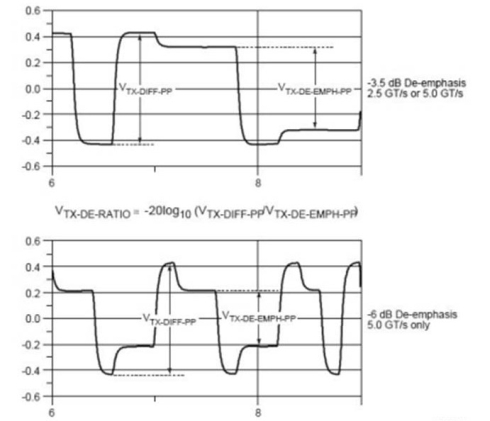

PCI Expressでは信号の立ち上がり、立ち下がり時間が遅くならないように、信号が「01」や「10」と変化する時には損失で高い周波数成分が失われる場合を除いて、すべての信号周波数成分の振幅を小さくして、レシーバに信号が到達した時にすべての周波数成分同じレベルで、到達するように工夫しました。これをデエンファシスと呼びます(図6)。

このように多くの工夫をして、基板でそれまで限界といわれていた1GHzを超える速度の信号伝送を可能としました。

この結果、配線やICの集積度が低くなり、コストも高価な光伝送を基板に導入することは見送られ、銅配線の時代が続くことになりました。

PCI Expressは2代目のGen2となり、信号の速度は倍の2.5GHzとなりました。この結果、基板配線の損失は大きくなり、プリエンファシスをさらに大きくする必要がありましたが、それ以上の大きな問題はなく簡単に基板配線で、2.5GHzが実現できました。

このPCI Expressの成功により、USBやSATA(Serial ATA=Serial Advanced Technology Attachment)、HDMI(High Definition Multimedia Interface)など、ほぼ同様の技術を使った多くのシリアルデータ転送バスが規格化されました。

しかし、次のPCI Expressの3代目規格PCI Express Gen3の規格化で問題が発生しました。

2.5GHzに比べ、5GHzの信号では、高価な低誘電率、低損失の基板材料を使わないと、回路だけでは損失がカバーしきれないほど大きくなってしまいました。

結局、PCI Express Gen3では5GHzをあきらめて信号速度を4GHzに落とす代わりにデータの符号化アルゴリズムを変えることにより、データ転送速度だけはGen2の2倍の速度を確保することで規格化されました。

ここで、4GHzが銅配線の限界に近いのかとの議論が生まれました。これ以上に速度では、高価な基板材料屋や、高価なコネクタなどの電子部品、EMI(電磁放射ノイズ)などへの対応から、銅を使ってもコストがアップし、光が競合できるのではないかという議論です。

この議論を背景にIntel社がLight Peak規格を提案し、光を積極的に推し進めてきました。ただし、Light PeakはUSB 3.0のようなIOバス規格で、基板内の配線を銅の配線パターンから光ケーブルに変えるというものではありません。また、Intel社はApple社と組んで、Light Peak規格を銅でも使えるようにしたThunderbolt規格に変更し、Apple社から銅線規格のThunderboltが製品化されました。

現在、IOバスに関してはこの5GHzでの銅ケーブルと光ケーブルが競っています。

それでは、基板内配線ではどうでしょう。IntelではThunderboltはIOバスに使い、基板内はPCI Express Gen3を使うとしています。また、さらに高速の次のPCI Express Gen4がうわさに上り始めましたが、銅での8GHz(16GT/s)の可能性について検討されています。現在、PCI Expressの規格化を行っているPCI SIGではシリコン基板を含めた新しい基板材料による高速化の検討はしているが、今のところ『光』については考えていないとのことです。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 品質保証とは何か、その定義を改めて考える

- タイの半導体製造工場で新棟が完成、ソニーセミコンが生産力を強化

- 三菱重工が航空機エンジン部品工場を増強、内製力強化で完全一貫生産を実現

- パワー半導体の電流測定が正確に、光プローブを用いた電流波形測定用センサー

- ルネサスが甲府工場で300mmウエハーライン稼働、パワー半導体の生産能力を2倍に

- 日立産機が三菱電機 名古屋製作所の配電用変圧器事業を譲受、2026年4月に統合完了

- 工場でCO2排出量1次情報をなぜ取得すべきなのか 85%以上の削減効果も

- 誤差9割、コストを抑えるためにもCO2排出量は測った方がよい

- OTセキュリティを巡るエネルギー業界の法改正とは、変わる事業者の事故対応

- IEC 62443とは何か、工場のサイバーセキュリティ対策のカギを握る国際標準を解説

図1 PCE Express基板規格

図1 PCE Express基板規格 図2 配線の損失を考慮した規格(出典:PCI Express Card Electromechanical SpecificationRevision 2.0 April 11, 2007)

図2 配線の損失を考慮した規格(出典:PCI Express Card Electromechanical SpecificationRevision 2.0 April 11, 2007)