第9回 TSVを前提としたモバイルDDR:前田真一の最新実装技術あれこれ塾(2/3 ページ)

3. LPDDR3

これまでのJEDECのモバイルメモリ規格の名称がLPDDR、LPDDR2とあったように、このLPDDR3規格はこれまでの規格を基にスピードアップを図ったものです。

JEDECによる一般のDDRメモリ規格にDDR2とDDR3があります。LPDDR2規格はDDR2規格を基に、モバイル用規格としましたが、LPDDR3規格はDDR3規格を基にしたものではなく、DDR2規格を基にした、LPDDR2規格の高速版です。

ここで、表1にDDR、DDR2、DDR3の規格とLPDDR、LPDDR2、LPDDR3規格の概略をまとめます。表には在りませんが、容量もLPDDR3はLPDDR2の2倍まで対応しています。

LPDDR3規格は単なるLPDDR2規格の速度を上げただけの規格になっているのは、急きょ、間に合わせで作られた規格だからです。

本来、JEDECでは、次のモバイルメモリには新しい技術を使って、高速化と低電力化を飛躍的に推し進めようとしていました。

しかし、これまでの製品の延長である、携帯電話やディジカメ、携帯音楽機器ではなく、スマートフォンやタブレット端末のような新しい携帯機器が急速に普及してきました。これまでの機器の発達であれば、新しいモバイルメモリ規格の制定までは、LPDDR2規格で間に合うと思われていたものが、新しく出現した機器に対しては、LPDDR2規格では、機能不足で、新しいモバイルメモリ規格の制定を待っていたのでは、間に合わなくなってしまったのです。

このため、急きょ、すぐに製品化できる技術を使って、メモリの高速化を主な目標に、消費電力は増えなければ良いという、LPDDR3規格を早急に決める必要に迫られたのです。

LPDDR3規格は来年(編注:2012年)中には規格も決まり、規格に対応したメモリも出現すると期待されています。

4. 発想の転換

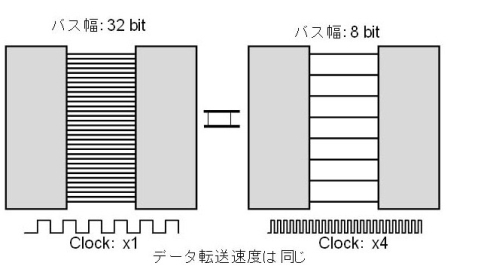

メモリバスを含めて、バスのデータ転送速度は、1ライン当たりの転送速度とバスのデータ幅の積になります(図2)。

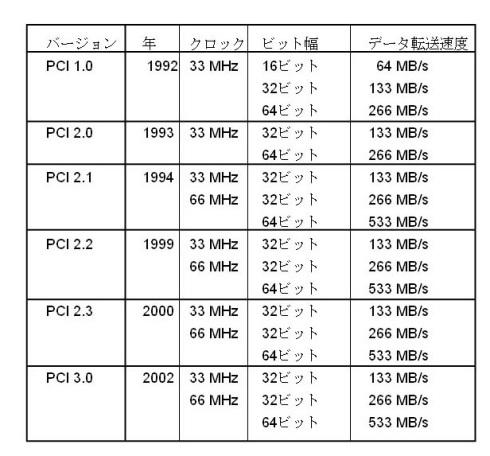

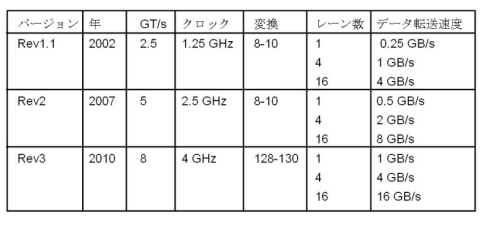

このため、PCIバスなどでは、バスのクロック速度を上げると同時にバスのビット数を増やしてデータ転送速度を上げてきました(表2)。

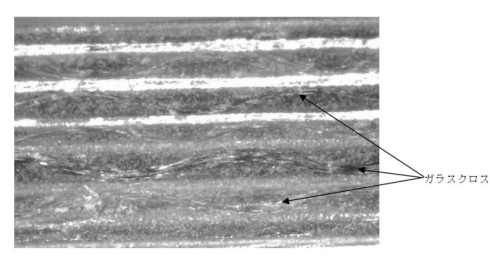

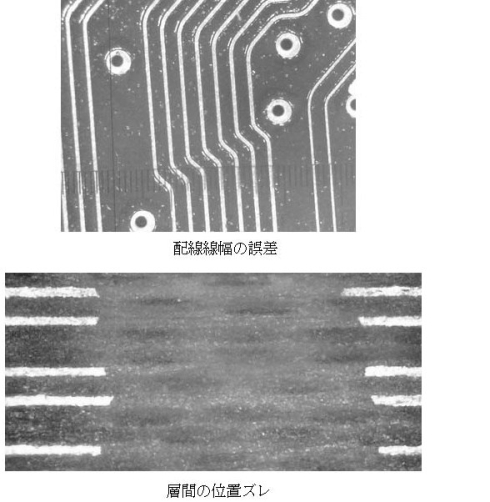

しかし、クロック速度の上昇に従って、多くのビットデータの同期が困難になって来ました。特に長い基板配線では、クロストークノイズやISIノイズ、基板のガラス繊維のむら(図3)や製造誤差(図4)による伝播遅延誤差など、多くの要因により、全く同じ配線長であってもデータライン間で発生する遅延誤差が制御しきれなくなりました(図5)。

このため、発想の転換が行われ、バスのビット幅を1ビットにして、クロック速度を上げて、データ転送速度を上げるシリアルデータ転送が登場しました。そして、このシリアルデータ転送ラインを複数、設けてデータ転送速度を上げるというものです。お互いのシリアルデータ転送ライン間ではデータの同期は必要ありません。

並列のPCIバスから直列のPCI Expressバスになり、データ転送速度が急激に高速化されました(表3)。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- PLCレスで協働ロボットの外部軸を制御、自動化システム構築の工数削減

- ラズパイの電源を入れてみた

- ハノーバーメッセが開幕、AIや水素など「競争力ある持続可能な産業」の最新技術

- 品質保証とは何か、その定義を改めて考える

- RYODENらが生成AIの事業応用で協業、現場映像と設備データの融合も目指す

- サーバなど向け、高風量かつ高静圧ながら連続運転10万時間の長寿命な冷却ファン

- IEC 62443とは何か、工場のサイバーセキュリティ対策のカギを握る国際標準を解説

- マレーシアで半導体ウエハーバンピングの受託加工向け製造装置増設

- タイの半導体製造工場で新棟が完成、ソニーセミコンが生産力を強化

- パワー半導体の電流測定が正確に、光プローブを用いた電流波形測定用センサー