第11回 LSI消費電力把握の必要性と試み:前田真一の最新実装技術あれこれ塾(2/3 ページ)

2. コンカレントエンジニアリング

一般にASICの開発には基板の開発に比べ、けた違いに多くのコストと時間が掛かります。

製品開発期間を短縮すると同時に設計品質を向上させるため、ASICチップの設計にめどが立った時点で、ICパッケージと基板の設計を開始します。

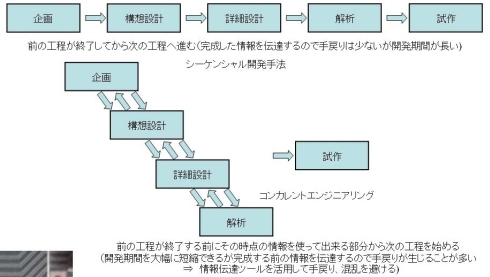

このようにチップとパッケージ、基板(システム)を同時並行で開発して行く手法をコンカレントエンジニアリングと呼びます(図8)。コンカレントエンジニアリングで重要なことは設計の早い段階から、お互いの情報を共有し、おのおのが調整しあって最適設計をすることにあります。

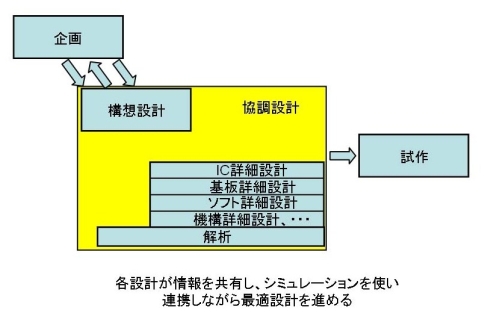

チップとパッケージ、基板(システム)に加えて、機構までを含めた設計プロセスの間情報をやり取りし協調して、最適設計を行うことを協調設計と呼びます(図9)。協調設計でお互いにやり取りする重要な情報の一つとして、ASICの消費電力情報があります。

ASICの消費電力はチップの発熱量の基本データで熱設計にはなくてはならないものです。協調設計ではASICの発熱量を基にパッケージ、基板、機構の熱設計を協調して行い、システム全体の合理的な熱設計がおこなえます。

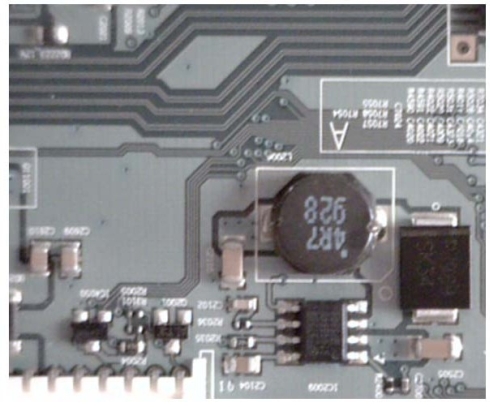

ASICの消費電力はASICに電力を供給する電源回路の設計にも必要不可欠な情報です。大電力を消費し、SSOノイズも大きなASICに対しては、基板上でASIC専用の電源回路を用意するようになっています(図10)。

この電源供給回路は、ASICの消費電力が分かれば最適設計ができますが、消費電力が不正確な場合、安全性を見込んで過大な供給電力回路を設計しなければなりません。

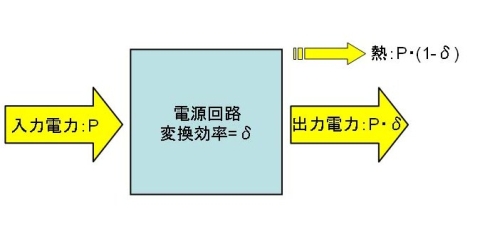

電源容量の大きな電源回路は、部品が大容量となり、大型化、高コスト化の原因になります。また、電源回路は100%の効率を持っているわけではないので、大容量化すると、電源回路自体の消費電力と発熱が増大します(図11)。

逆に電源回路の容量が小さいと、容量不足のためSSOノイズが増大したり、過負荷による発熱や寿命の低下を招いたりします。消費電力の変化量と、変化速度を知ることはSSOノイズ対策にとって、重要な情報です。

この情報を使うことによりバイパスコンデンサの容量や配置の最適設計ができます。また、この情報から、精度の高いSSOノイズの解析が行えます。また電源電圧の変動は大きなEMI放射の原因となります。EMI対策からも、ASICの消費電力変化を把握して、電源電圧の安定化を図ることは重要です。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 品質保証とは何か、その定義を改めて考える

- 三菱重工が航空機エンジン部品工場を増強、内製力強化で完全一貫生産を実現

- タイの半導体製造工場で新棟が完成、ソニーセミコンが生産力を強化

- 日立産機が三菱電機 名古屋製作所の配電用変圧器事業を譲受、2026年4月に統合完了

- ルネサスが甲府工場で300mmウエハーライン稼働、パワー半導体の生産能力を2倍に

- 工場でCO2排出量1次情報をなぜ取得すべきなのか 85%以上の削減効果も

- パワー半導体の電流測定が正確に、光プローブを用いた電流波形測定用センサー

- 工場のスマート化で高まるサイバーリスク、経産省が対策の要点など公開

- 誤差9割、コストを抑えるためにもCO2排出量は測った方がよい

- IEC 62443とは何か、工場のサイバーセキュリティ対策のカギを握る国際標準を解説

図11 電源の変換効率

図11 電源の変換効率