第13回 TSVが量産技術へ〜Wide I/O規格:前田真一の最新実装技術あれこれ塾(1/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第13回は、JEDECが2011年末に規格内容を正式に発表した、次世代メモリインタフェース「Wide I/O」について説明する。

本連載は「エレクトロニクス実装技術」2012年4月号の記事を転載しています。

1. モバイルメモリ規格Wide I/O

かねて噂になっていたモバイル用メモリの新しい規格、Wide I/O Single Data Rate(Wide I/O SDR)/JESD229が昨年の年末(2011年末)にJEDEC(JEDEC Solid State Technology Association)から発表されました。JEDECは半導体部品規格の標準化を行っている業界団体で、事実上、半導体部品の世界標準規格を規定している団体です。

このWide I/O規格は、JEDECが過去に制定した、DDR2メモリ規格(JESD79-2)、DDR3メモリ規格(JESD79-3)、モバイル用のLPDDR規格(JESD209)、LPDDR2規格(JESD209-2)などを踏まえて作成した新しい規格です。

実はこのWide I/O規格の他に、同じモバイル用メモリ規格として、LPDDR3規格も同時に策定されています。LPDDR2規格は単純に現在のLPDDR2規格を高速化したもので、Wide I/O規格よりも先に発表されると考えられていました。しかし、実際にはLPDDR2規格に比べ、多くの新しい技術が盛り込まれた、このWide I/O規格の方が早くリリースされました。LPDDR3規格もまもなく発表されるものと思われます。

Wide I/O規格はTSVを始め、多くの新しい技術が導入されているので、Wide I/O規格メモリが安定してリリースされるのは遅れるだろうと考えられています。それに対し、LPDDR3規格は現在のLPDDR2規格の高速版ということで、製品はLPDDR3規格がすぐに出てくるのだろうと見られています。

Wide I/O規格のメモリを速く市場に出すためにも、規格のリリースを少しでも早くしたものだと思われています。

このため、今回の規格では、細かい仕様は制定されていません。とりあえず、仕様を公開し、メモリベンダやコントローラベンダが製品開発が出来るようにしたものと思われます。

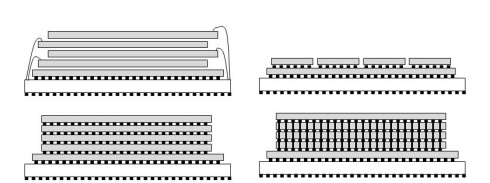

Wide I/O規格の特徴はメモリチップを垂直方向に2段から4段の3次元実装を行うことを規格に盛り込んでいることです。

2. TSVが前提の規格

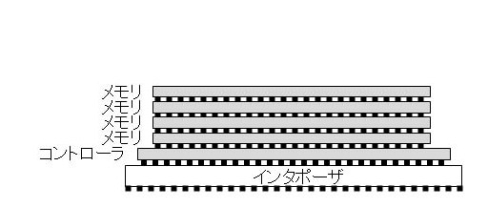

Wide I/O規格では、コントローラチップを下にして、その上にメモリチップを最大4枚まで積層(Stack)して実装規格になっています(図1)。

おのおののメモリチップはスライス(Slice)と呼びます。

規格的にはチップの3D実装は定義していますが、この3D実装を実現するための方法については規格化していません。TSVを使っても旧来のワイヤボンディングを使っても規格的には満足できます(図2)。

しかし、実際のピン数やピンのピッチなどからはTSVを使った実装を想定しています。実際、JEDECによるWide I/O規格の説明会資料でもTSVをうたっています。

モバイル用メモリと言う大量生産の汎用部品にTSVを使う規格が制定されたことにより、TSV技術は、高機能部品用のニッチマーケットから汎用部品のメインストリーム製品の技術へと立場を変えました。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 品質保証とは何か、その定義を改めて考える

- 三菱重工が航空機エンジン部品工場を増強、内製力強化で完全一貫生産を実現

- タイの半導体製造工場で新棟が完成、ソニーセミコンが生産力を強化

- ルネサスが甲府工場で300mmウエハーライン稼働、パワー半導体の生産能力を2倍に

- パワー半導体の電流測定が正確に、光プローブを用いた電流波形測定用センサー

- 日立産機が三菱電機 名古屋製作所の配電用変圧器事業を譲受、2026年4月に統合完了

- 工場でCO2排出量1次情報をなぜ取得すべきなのか 85%以上の削減効果も

- 誤差9割、コストを抑えるためにもCO2排出量は測った方がよい

- OTセキュリティを巡るエネルギー業界の法改正とは、変わる事業者の事故対応

- IEC 62443とは何か、工場のサイバーセキュリティ対策のカギを握る国際標準を解説

図1 Wide I/Oメモリの構造

図1 Wide I/Oメモリの構造