Intelの14nmプロセスとARM「Cortex-A53」を採用、Alteraの「Stratix 10 SoC」:ビジネスニュース 企業動向

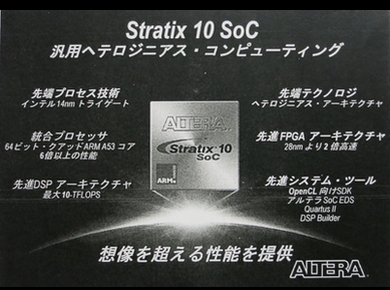

Alteraは、次世代SoC FPGA「Stratix 10 SoC」のCPUコアに、最大4コアの64ビットプロセッサ「ARM Cortex-A53」を採用する。Stratix 10 SoCはIntelの14nmトライゲートプロセスで製造されるため、ARM Cortex-A53は従来のデュアルコアプロセッサ「ARM Cortex-A9」に比べて、少なくとも6倍のデータ処理能力が得られるという。

Alteraは2013年10月29日(米国時間)、次世代SoC(System on Chip) FPGA「Stratix 10 SoC」のCPUコアに、最大4コアの64ビットプロセッサ「ARM Cortex-A53」を採用すると発表した。Stratix 10 SoCは、Intelの14nmトライゲートプロセスで製造されるため、ARM Cortex-A53は従来のデュアルコアプロセッサ「ARM Cortex-A9」に比べて、少なくとも6倍のデータ処理能力が得られるという。Stratix 10 SoCは2014年10月以降にテープアウトされる予定である。

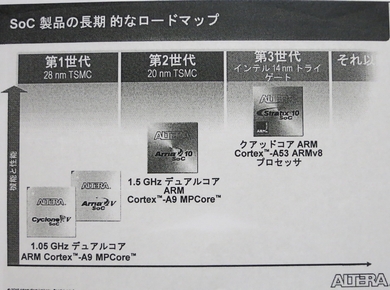

同社は、2013年6月に「Generation 10 FPGA&SoC」の概要を発表した。Intelの14nmトライゲートプロセスで製造されるハイエンド製品の「Stratix 10」と、TSMCの20nmプロセスを用いて製造されるミッドレンジ製品「Arria 10」である。その時点では、「Arria 10 SoC」は動作周波数が1.5GHzのデュアルコアプロセッサ「ARM Cortex-A9」を採用すると発表していたが、Stratix 10 SoCに搭載するプロセッサコアについては、これまで明らかにしていなかった。

ARM Cortex-A53は、64ビット命令を含むARM v8命令セットアーキテクチャをベースとしたプロセッサコアで、同じ64ビットコアの「ARM Cortex-A57」に比べて小型・省電力コアというのが特長だ。Intelの14nmトライゲート技術と組み合わせることで、従来のARM Cortex-A9を搭載したSoC FPGAに比べて少なくとも6倍のデータ処理能力を実現できるという。また、32ビットモードでの動作も可能で、ARM Cortex-A9を搭載したSoC FPGAとのソフトウェア互換性もある。ただ、今回はARM Cortex-A53コアの動作周波数や、CPUコアとメモリコア間あるいはIPコアと接続するオンチップバス規格など、チップの詳細については明らかにしなかった。

Stratix 10 SoCは、ロジック部の動作周波数を1GHz以上にすることが可能となり、28nmプロセスで製造されるStratix Vに比べて2倍の性能となる。また、DSPブロックには、ハードウェア化された浮動小数点DSPを実装することで、最大10テラFLOPSの演算性能を実現することが可能である。

Alteraでエンベデッドプロセッシングマーケティング担当のシニアディレクタを務めるChris Balough氏は、ARM Cortex-A53を選択した理由について、「ロジック部やDSP部の性能を考慮し、ヘテロジニアスコンピューティングを実現するための最適なCPUコアを選んだ。これによって『高い演算性能』と『低い電力消費』という2つの目標を達成できた」と話す。さらに、「ARM Cortex-A53は汎用性があり、今後はミッドレンジのSoC FPGAのCPUコアにも利用できる」と述べた。

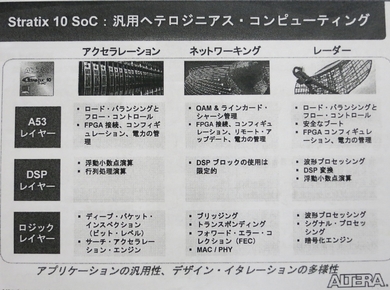

Balough氏は、Stratix 10 SoCのシステム応用について、3つの事例を挙げた。「データセンターアクセラレーション」、「ネットワーキングとデータ伝送」および「レーダー」である。いずれも、システムのコントロールプレーンに実装されているホストプロセッサの演算負荷が増大する中で、その負荷をStratix 10 SoCが実装されたラインカードなどに分配することができる。これによって、設備の投資費用や電力消費を抑えつつ、システムの処理能力を向上させることが可能となる。

Alteraは、SoC FPGAのソフトウェア開発環境も用意している。並列処理を行うヘテロジニアスコンピューティングシステム向けのプログラミングツールとして「OpenCL向けソフトウェア開発キット(SDK)」がある。FPGA用に最適化されたツールでOpenCLソフトウェアからハードウェアを生成することができる。また、「ARM DS-5 Altera Editionツールキット」を含むAlteraの「SoCエンベデッドデザインスイート(EDS)」を用いると、ヘテロジニアス構成のチップ全体のデバッグや可視化が可能になるという。

- もうスマホでやけどしない!? 薄さ100μmの断熱シート

- インテル、大規模な人員削減か

- 壊れにくい抵抗器、小さいディスクリート――独自色打ち出し、国内車載市場へ浸透へ

- 試作に特化する通販代理店マウザーが日本にサポート拠点を開設

- 新生Broadcomに向け準備着々、一部事業売却の可能性も?

- Industry4.0に向けた製品戦略を加速、リファレンスデザインで開発支援

- 年功序列廃した“機動力ある1000人体制”で挑む新生サイプレスの国内戦略

- ユーブロックス、大阪にオフィスを開設

- スマートグラスで視覚障がい者の外出をサポート、現在地を遠隔地でもシェア

- AppleがARメーカーを買収、車載市場参入に本腰?

関連記事

全ての機器にアルテラ製品を、多様な製品群で自動車/産業機器分野に挑む

全ての機器にアルテラ製品を、多様な製品群で自動車/産業機器分野に挑む

大手FPGAベンダーのアルテラは、2013年後半から2014年にかけ、さまざまな新製品投入を予定する。14nmという最先端プロセス採用品から55nmフラッシュメモリ内蔵の低コストファミリ、さらには電源ICをも手掛ける。取り扱い製品が多様化しつつある中、2013年7月に日本アルテラの社長に就任したハンス・チュアン氏は、「全ての製品にアルテラ製品を搭載する」という。チュアン氏に日本法人社長としての抱負や事業戦略を聞いた。 シリコンコンバージェンスを可能とするアルテラSoC、開発環境も整う

シリコンコンバージェンスを可能とするアルテラSoC、開発環境も整う

FPGAベースの設計手法は、設計の柔軟性を確保しつつ最先端プロセス技術を活用できることから注目を集めている。こうした中で「シリコンコンバージェンス」を提唱しているアルテラは、最先端FPGA技術をベースとしたSoC設計を推進している。 「20nmまではTSMC、14nm以降はIntel」、Alteraが製造戦略を説明

「20nmまではTSMC、14nm以降はIntel」、Alteraが製造戦略を説明

Alteraは次世代FPGAについてIntelの14nmトライゲート技術の採用を決め、Intelに生産委託する契約を締結した。Alteraではこの技術を最上位のFPGA製品に適用し、「これまでの技術では成しえなかった性能や機能を実現していく」考えだ。 Intelの14nmプロセス技術を用いた「Stratix 10」を発表、年内にテストチップ出荷

Intelの14nmプロセス技術を用いた「Stratix 10」を発表、年内にテストチップ出荷

アルテラは次世代FPGA「Generation 10」として、Intelの14nmトライゲートプロセスで製造するハイエンド製品「Stratix 10」と、TSMCの20nmプロセスを用いたミッドレンジ製品「Arria 10」を発表した。Stratix 10は、現行のStratix Vに比べて性能が2倍となる。

Copyright © ITmedia, Inc. All Rights Reserved.

Alteraの「Stratix 10 SoC」のパッケージ外観

Alteraの「Stratix 10 SoC」のパッケージ外観

Alteraでエンベデッドプロセッシングマーケティング担当のシニアディレクタを務めるChris Balough氏

Alteraでエンベデッドプロセッシングマーケティング担当のシニアディレクタを務めるChris Balough氏