FPGAとASICの特長を兼備するカスタムLSI「TeneX」が待望の高速トランシーバを搭載:丸文 TeneX-GX

「カスタムLSIの開発期間を短縮し、設計やチップのコストを節減したい。消費電力ももっと小さくしたい」。技術商社の丸文は、こうしたIC設計者の要求に対して提案しているのが、FPGAとASICの特長を兼ね備える「TeneX」だ。このTeneXに、最大6.5Gビット/秒のトランシーバを搭載した新製品「TeneX-GX」が登場した。

エレクトロニクス技術商社の丸文は、米国のファブレス半導体メーカーであるBaySandのマスタスライス型ASIC「TeneX-GX」の受注を始めた。FPGAの柔軟性とASICのコストメリット、両方の利点を兼ね備えており、高い演算性能と低消費電力も実現できることから注目を集めている。さらに、開発費やチップコストの節減、開発期間の短縮も可能だ。今回受注を開始したTeneX-GXは、従来品の「TeneX」に伝送速度が最大6.5Gビット/秒のトランシーバ機能を追加した製品で、高速シリアルインタフェースを必要とする画像処理や通信機器に提案していく。

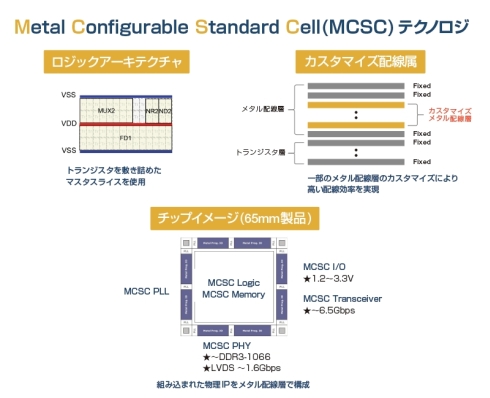

メタル配線層のカスタマイズだけでカスタムLSIが完成

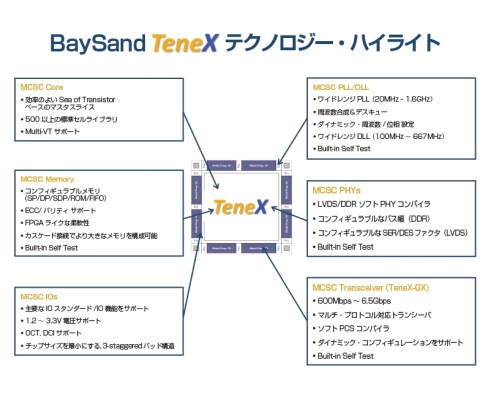

TeneXは、あらかじめ製造しておいたユニークなSea-of-Transistor型のマスタスライスを、一部のメタル配線層のみをカスタマイズして回路を構成することにより、設計者の求めるカスタムLSIを完成させられるIC製品である。開発元のBaySandはこの技術を、「Metal Configurable Standard Cell(MCSC)テクノロジ」と呼ぶ。チップ内部にはトランジスタを全面に敷き詰めたロジック部に加え、FPGAライクな柔軟性を持つSRAM、PLL(位相同期回路)やさまざまな電圧レベルに対応可能な入出力インタフェースといったマクロが埋め込まれている。この他、LVDSインタフェースやDDRインタフェースにも対応。新製品のTeneX-GXでは、トランシーバを担うSERDES(シリアライザ/デシリアライザ)回路も集積されている。

MCSCテクノロジは、ゲートアレイ型ASICを進化させたストラクチャードASICと構造が似ている。ただし、マスタスライスとして「論理ゲート」ではなく「トランジスタ」を敷き詰めている点が異なる。これによって、「従来のストラクチャードASICよりも効率的に回路を構成できる上、回路の動作周波数を高めることができる」(丸文)という。製造はファウンドリ専業のGLOBALFOUNDRIESに委託しており、第1世代に当たる「TeneX」と「TeneX-GX」は、同社の65nmプロセスを用いて生産される。

ASICやFPGAには一長一短がある

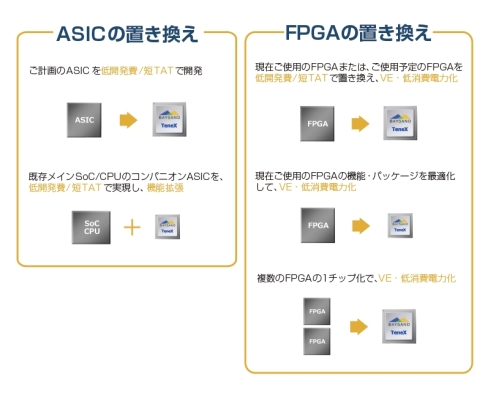

これまで、特定用途や顧客仕様のLSIを設計するためには、ゲートアレイやスタンダードセルと呼ばれる一般的なASICや、あるいはFPGAを用いるのが一般的だった。しかし、これらのLSIには一長一短がある。例えば、ゲートアレイ型ASICは開発費が比較的低く抑えられるが、回路規模や性能面で十分に対応し切れないことが多い。スタンダードセル型ASICは、一定規模の量産規模を確保できる場合には製造コストが安価になるが、プロセスの微細化によって高騰している設計/開発費がネックになる。その上、回路が大規模となるため設計期間も長期化する傾向が強い。一方、開発の柔軟性などから急速に需要が拡大しているFPGAは、ASICに比べてチップ単価が高く、消費電力も大きい、といった課題を抱えている。

TeneXは、効率の良いセル配置や配線を可能とするMCSCテクノロジにより、最適化されたチップサイズを実現し、パフォーマンスが高く、消費電力の小さいカスタムLSIを、比較的短期間で開発することが可能となる。しかも、開発費や量産時のチップコストも節減できるなど、従来のASICとFPGAの特長を兼ね備えたLSIといえるだろう。

丸文は、「一部最適化は必要だが、RTLで記述された設計データを顧客からいただければ、その3カ月後にはエンジニアリングサンプル品を出荷することができる。お客様の設計内容にもよるが、その開発費は3000万〜4000万円程度で済ませることも可能だ」としている。実際に、「あるユーザーがカスタムLSIの開発コストを見積もったところ、スタンダードセル型ASICで約1億円と言われた案件が、TeneXではその半額以下に抑えられた」、「バッテリーアプリケーションにFPGAを使用していたユーザーの場合、TeneXへの置き換えによって消費電力を3分の1に削減され、機器の発熱を最小限に抑えることができ、バッテリーの持ち時間も大幅に延ばすことができる見込みである」(丸文)といった事例がある。また、目安として使用量が年間に1万個を超える用途であれば、FPGAよりもTeneXの方がコストメリットを得られるという。

第1世代のTeneXは2012年に発表され、日本の総代理店である丸文が販売している。今回発表したTeneX-GXは、TeneXをベースとしたもので、伝送速度が最大6.5Gビット/秒のSERDES回路が新たに実装された。これにより、PCI ExpressやシリアルATA、Serial Rapid I/O(SRIO)、Common Public Radio Interface(CPRI)、ギガビットイーサネットといったプロトコルに対応する高速シリアルインタフェースを容易に実現できるようになった。

TeneX-GXは、内部コアロジックのパフォーマンスでも優れている。一般的にASICはスタンダードセル型が高性能といわれているが、TeneX-GXもほぼ同等の性能が得られる。また、FPGAと比べた場合には、28nm世代のFPGAに相当するパフォーマンスは優に確保できるとする。

TeneXとTeneX-GXは、大手FPGAベンダーが通信機器や産業機器、民生機器などに向けて展開している一般的な製品とピン互換性を備えた品種を用意している。回路規模の大きい特殊なFPGAについても、個別案件としてピン互換対応が可能だとしている。これによって、機器の量産時に、FPGAからTeneXやTeneX-GXへの置き換えが比較的容易に行えるというわけだ。

40nmプロセス採用の次世代品も計画中

BaySandは、65nmプロセス技術を使った第1世代の2製品に続いて、2014年中には40nmプロセス技術を用いた第2世代品を市場投入する計画を明らかにしている。現時点で製品に関する詳細な情報は開示されていないが、標準品を2014年7月以降(第3四半期)に、伝送速度が最大12.5Gビット/秒のトランシーバを搭載する製品を同年10月以降(第4四半期)に、それぞれ発売する予定である。メモリインタフェースについては、第1世代品がDDR3-1066以下となっていたが、第2世代品ではDDR3-1066を上回る高速インタフェースをサポートしていく計画だ。

FPGAやスタンダードセル型ASICを活用しているユーザーで、開発期間の短縮やコストの節減、消費電力の低減などに取り組んでいる設計者は、TeneX/TeneX-GXの採用を一度検討してみてはいかがだろうか。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:丸文株式会社

アイティメディア営業企画/制作:MONOist 編集部/掲載内容有効期限:2014年9月18日

関連記事

ASICは今、プロセス技術の微細化に伴って開発費と開発期間が膨らんでおり、一部がFPGAに移行している。ただしFPGAは、チップ単価だけを比較するとASICよりも高くつく。そこで技術商社の丸文は、米国の新興ベンダーの新型ストラクチャードASICを提案し、“FPGAからASICへ”という逆潮流を生み出すことを狙う。