「SoC」or「SoC」?統合へのさまざまな道:SYSTEM DESIGN JOURNAL(1/4 ページ)

1つのダイに複数機能を実装するSoC(System on Chip)化の波は高まるばかりです。アーキテクトはダイ間接続とマルチダイパッケージングの動向に注意を払い、コストや消費電力、将来性までも視野に入れた選択をしなければなりません。

SoC(System on Chip)は、1つのダイに搭載可能なものは全て搭載することです。マルチダイ統合アプローチを採用する正当な理由としては、技術不足、主要プロセスの非互換性、または物理的なスペース不足しかありませんが、そうした考え方は終わりつつあります。

現在、より低コストのマルチダイパッケージング、高速シリアルトランシーバーの画期的利用、さらには非電気的インタコネクトをはじめとする新たな選択肢により、複数のダイにわたるシステムコアのパーティショニングに関して新たな可能性が開かれています。

アーキテクトは以前ならば帯域幅の制約や消費電力のせいで除外してきたアイデアを検討できるようになります。つまり、現在の市場の状態よりはるかに優れた性能、効率、コンパクトさの新たな組み合わせにつながるかもしれないということです。

パーティショニング

複数のダイにまたがるシステム分散について説明するに当たって、まずパーティショニングの話から始めなければなりません。検討可能な選択肢は、サブシステム間リンクに必要な帯域幅とレイテンシによって決まります。

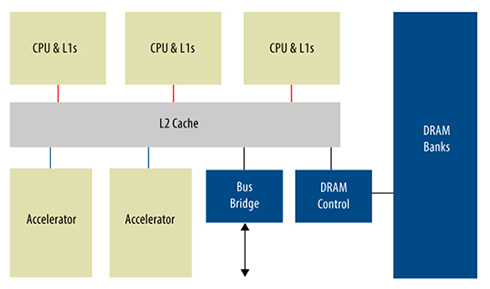

この2つのパラメータを区別することが重要です。広帯域な同期バスにおいて帯域幅とレイテンシは、どちらかといえば逆の関係にあり、バスが高速なほどレイテンシは低く、帯域幅は広くなります。しかし、ストリーミングインタフェースや高速シリアルリンクは、レイテンシの増加を受け入れないと帯域幅を拡大できないことがあります。従って、サブシステム間の各リンクの状況を理解することが重要です(図1)。

つまり、レイテンシが重要なのか、帯域幅が制約なのか、あるいはその両方なのか、ということです。ブロック間の接続に対する制約が最も少なくなるように、システムをパーティショニングしようとするのが一般的です。そうすれば、SoCまたはFPGAデザインのフロアプランニングや、システムを複数のダイ間に細分する際に最大限の自由度が得られるからです。

オンチップ/チップ間のいずれも最も効率的なインタコネクト手法は広帯域幅ですが、初期レイテンシが長いことから、ブロックをできる限りレイテンシの影響を受けにくくすることが非常に重要です。

当然、遅延増が絶対に認められないアプリケーションもあります。例えば、制御ループ内部のレイテンシは少し増加するだけで、システムが臨界減衰から不安定になることがあります。そのような場合、全てのブロックをループ内に統合するか、あるいはコストと消費電力を費やしてダイ間を幅の広いパラレル接続で結ぶ以外、選択肢はないかもしれません。

一方、レイテンシはあまり問題にならないが、スループットは重要というシステムもあります。そうしたシステムの一部は長いデータストリームを処理するもので、信号処理や一部の画像処理が挙げられます。

この種のコンピューティングは、多くの場合、予測可能な遅延の影響を比較的受けにくいパイプライン・アーキテクチャ実装することができます。ほとんどのパイプラインでは、インタコネクトのレイテンシは入力と出力の間の遅延にのみ影響し、パイプラインの帯域幅には影響しません。

また、アルゴリズムを簡単にパイプライン化することはできないものの、多数のスレッドに分解することは可能という場合もあります。いつでも実行可能なスレッドが十分にあれば、現在のスレッドがストールしたらすぐに別のスレッドを取り上げることにより、非常に長く予測不能なレイテンシでもカバーできます。

最新のCPUコアではある程度まで利用できることが多く、GPUでは驚くほど深いハードウェア・マルチスレッディングは、スレッド・スイッチングのオーバーヘッドを限定します。従って入力から出力に変化が生じるまでの間の遅延は長く、予測不能かもしれませんが、システム全体のスループットは高く、内部レイテンシとはほぼ無関係になります。

しかしながら、まずはやってみて遅延の増加に耐えることで、長いインタコネクトパスを補償するか、GALS(Globally Asynchronous,Locally Synchronous)ネットワーク・オン・チップを採用するか、あるいは一部のブロックを別のダイに移動するように、システムを再パーティショニングすることが可能になります。この記事の後半では、マルチダイ・システムにおいて別のダイにリンクする方法に焦点を当てます。

関連記事

組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングを加速させるハードウェア・アーキテクチャとは何でしょうか。DSP?GPU?それともメニーコアでしょうか。どのアプローチが最も適するのかを考察します。 FinFET革命がコンピュータアーキテクチャを変える

FinFET革命がコンピュータアーキテクチャを変える

FinFETの登場により、ムーアの法則はまだ継続される見通しです。ですが、それで全てが解決するわけではありません。FinFETの登場が、大きなSoCを自律的な機能ブロックに分割するという方向に導く結果となるでしょう。 サブシステムIPがチップの境界を越える

サブシステムIPがチップの境界を越える

サブシステム規模のIP(サブシステムIP)はSoCはもちろん、FPGAにまでも影響を与えています。素晴らしい取り組みですが、さまざまな注意点も存在します。スムーズな実装を行うための4つの注意点について述べます。 畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークとは何でしょうか。学問の世界から現実の世界に登場しつつあるこれは、さまざまな組み込みシステムに利用される可能性が高く、大いに関心を持つべきです。 組み込みにおけるコンピュータビジョンを整理する

組み込みにおけるコンピュータビジョンを整理する

画像認識(コンピュータビジョン、マシンビジョン)の需要は高まっており、その方法はさまざまです。画像による入力を有用なものとする実装方法について分類と整理を試みます。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 低価格FPGAでも文字認識AIの学習は可能なのか

- インフィニオンのSiC-MOSFETは第2世代へ、質も量も圧倒

- 組み込みシステム向けRTOSのシェアはTRON系が約60%

- パナソニックの電動アシスト自転車にエッジAI機能を提供

- スバルが次世代「EyeSight」に採用、AMDの第2世代「Versal AI Edge」

- イチから全部作ってみよう(7)正しい要求仕様書の第一歩となるヒアリングの手順

- CAN通信におけるデータ送信の仕組みとは?

- 自社開発のRISC-V CPUコアを搭載した32ビット汎用マイコン

- 東武ストアが指静脈による手ぶら決済を開始、酒類対応でセルフレジ利用率60%も

- CANプロトコルを理解するための基礎知識