インテルアーキテクチャもディープラーニングに有効、「GPUが最適は先入観」:人工知能ニュース(2/3 ページ)

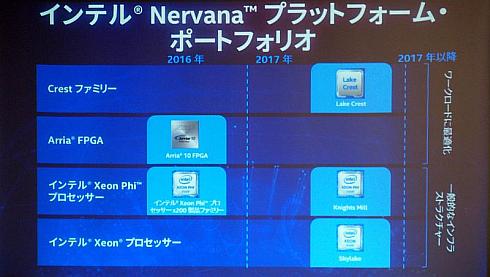

Nervanaはこの「スケーリング」を重視したAIプラットフォームである。まず基礎にくるのは汎用プロセッサであるXeonだ。次世代マイクロアーキテクチャである「Skylake」の初期開発版を出荷しており、2017年には量産投入されることになる。

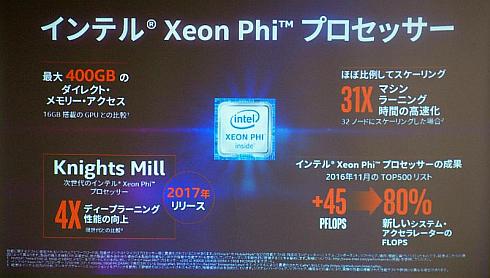

コードネーム「Knights Landing」として開発されたメニーコアプロセッサ(コア数は64)「Xeon Phi」は、最大400GBのダイレクトメモリアクセスや、マシンラーニング時のスケーリングが32ノードの場合に処理能力が31倍とほぼ比例していることなどを特徴としている。2017年には、単精度処理を強化してディープラーニング性能を従来比で4倍に向上したコードネーム「Knights Mill」の投入も予定している。

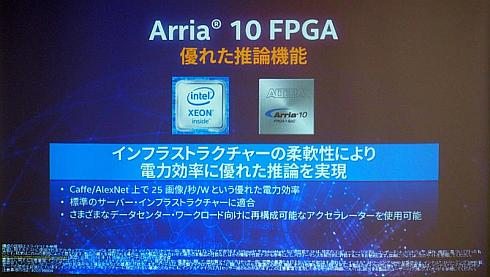

またXeonは、Altera(アルテラ)の買収によって加わったFPGAと組み合わせることで、マシンラーニングの推論向けに高い応答性と消費電力低減が可能になる。適用FPGAとしてはミッドレンジの「Arria 10」を想定している。

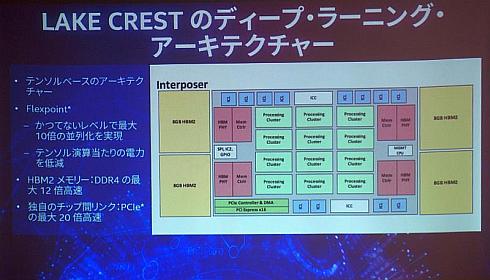

そしてディープラーニングに特化したソリューションとして、買収したナーバナ・システムズの技術を適用したアクセラレータチップである「Lake Crest」を2017年前半に最初のテストチップのデモを実施し、2017年後半には「数社の限定的な顧客」に先行納入する。このLake Crestは、Xeonと組み合わせるディスクリートICだが、将来的にはXeonとLake Crestの機能を統合した「Knights Crest」を投入する計画である。「Knights Crestの投入により、2020年までにマシンラーニングの時間を100分の1に短縮するという目標を達成する」(根岸氏)としている。

Lake Crestは、ディープラーニングの研究開発で広く用いられているGPUよりも優れた処理能力を発揮できる。テンソルベースのアーキテクチャと、ディープラーニングにおけるニューラルネットワークの畳み込み処理を精度が必要な場合とそうでない場合に合わせてフレキシブルに実行する「Flexpoint」と呼ぶ技術を組み合わせた。DDR4と比べ最大12倍高速なHBM2メモリ(32GB)などを含めて、1個のインターポーザ上に集積するという。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 低価格FPGAでも文字認識AIの学習は可能なのか

- インフィニオンのSiC-MOSFETは第2世代へ、質も量も圧倒

- 組み込みシステム向けRTOSのシェアはTRON系が約60%

- パナソニックの電動アシスト自転車にエッジAI機能を提供

- スバルが次世代「EyeSight」に採用、AMDの第2世代「Versal AI Edge」

- イチから全部作ってみよう(7)正しい要求仕様書の第一歩となるヒアリングの手順

- CAN通信におけるデータ送信の仕組みとは?

- 自社開発のRISC-V CPUコアを搭載した32ビット汎用マイコン

- 東武ストアが指静脈による手ぶら決済を開始、酒類対応でセルフレジ利用率60%も

- CANプロトコルを理解するための基礎知識