いまさら聞けない FPGA入門:半導体技術解説(2/3 ページ)

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部)

FPGAの方式について

現在はSRAMメモリセル方式が主流のFPGAですが、それ以外にもさまざまな方式のFPGAがあります。

1980年代後半、SRAM型FPGAとは異なる発想の「ヒューズ方式」(アンチヒューズFPGA)が登場しました。ヒューズ方式は回路の接点がヒューズになっており、ヒューズを焼き切ることで回路を形成します。アンチヒューズ素子は1回だけプログラム可能な記憶素子で、いったんプログラムすれば低抵抗で導通します。SRAM素子よりコンパクトなため高集積が可能であり、低抵抗で高速に動作できるといわれていました。その代わり書き換えは不可能で、何度も繰り返して使うことはできませんでした。また、低価格化しづらい点もデメリットでした。

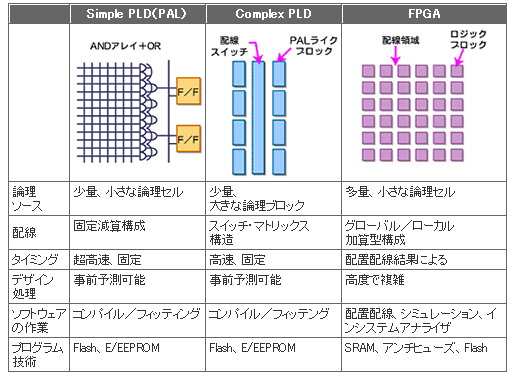

同時期に、もう1つのデバイスである「CPLD」(Complex PLD)が登場しています。これは、複数個の小規模なPLDを1個のLSIに集積することにより、任意の大規模論理回路を実現できるようにしたPLDです。小規模PLDと同じように、不揮発でありつつ書き換えが可能という使い勝手の良さが最大の特徴でした。その代わり、設計自由度の高さではFPGAに及びませんでした。

1990年代には、Flashメモリ技術を使用した「フラッシュFPGA」が登場しました。フラッシュFPGAは、書き換え可能というSRAM方式の利点と、不揮発性というアンチヒューズFPGAの利点を兼ね備えています。しかし、その構造と製造プロセスの複雑さから、集積度を引き上げること、価格を下げることが困難でした。従って、大容量・高速動作が要求されるFPGAには、あまり用いられませんでした。

現在の主流は、高速・大規模な場合はSRAMベースFPGA、そこまで高速性や規模が必要でない場合は、使い勝手の良いCPLDです。どちらもその構造上、製造性がよく安価にしやすいところも利点です。

FPGAの仕組み

さて、ここからは、具体的なFPGAの仕組みを説明します。最初は、論理回路の基になるプログラムの話です。FPGAのプログラムはどこにあるのでしょうか? SRAM型の場合はFPGAの外、つまり外部記憶メディアであるFlashメモリやEEPROMなどに記録されています。

SRAM型FPGAに電源が投入されると、この外部記憶メディアからプログラムファイルがロードされます。ここで呼び出されるプログラムファイルを「ビットストリームデータ」と呼びます。この情報は、FPGA内の1bit列のSRAM型メモリセルで構成されているコンフィグレーションメモリにロードされます。ロードされたビットストリームデータの個々のbitがFPGA上で実現するユーザー回路の情報元となり、FPGAに装備されているリソースをカスタマイズしてユーザー所望の回路を実現するのです。PCなどにおけるCPUのブートプロセスと非常によく似ています。ハードウェアに依存せず、コンフィグレーションデータを外部に持つことで、高い汎用性とフレキシビリティを実現しているのです。

次に、FPGAの内部構造を説明します。FPGA内は、

- I/O部

- 内部配線

- ロジックセル

- クロックネットワーク

- JTAGバウンダリ・スキャン回路

- ブロックRAM・乗算器

の6つの部分に大別できます(図3)。

まず、FPGAの特徴である「ロジックセル」について説明します(図4)。FPGAのロジックセルは、一般的に4あるいは6入力の「ルックアップテーブル」(Look Up Table:以下LUT)と「フリップフロップ」(Flip Flop)の2つから構成されています。

SRAMのアドレスに当たる入力部分に信号が来ると、その組み合わせに応じてLUTに記憶されているデータを出力する仕組みです。

図4は、ANDとして使う場合を示しています。アドレスがすべて1になる場所にHigh(1)のデータ、それ以外にはLow(0)のデータが書き込まれています。そこで入力がすべて「1」のとき、データとして保持されている「1」が出力されます。その後、フリップフロップによりシステムに同期したタイミングでデータが出力されます。ロジックセルはFPGAの全面に分散して配置されており、これらを内部配線でつなげていくことによりユーザーの希望するファンクションを実現します。

「I/O部」は主にFPGAの周辺部に位置しており、外部との信号のやりとりをします。現在では、20種類を超えるさまざまな電圧レベル・規格に対応できるフレキシブルなI/Oが提供されており、自由にボード上の配線を実現できるポイントになっています。

「内部配線」部分は、ロジックセル間やI/O部を結合してユーザーのファンクションを実現します。

「クロックネットワーク」は、FPGA内のクロックを配分するためのリソースです。FPGA全体に提供するクロックと、局所的に使用するクロックの2種類が提供されており、各所で最適な回路動作を実現します。特に、同期回路の設計に必須なのがクロックネットワークです。

「JTAGバウンダリ・スキャン回路」部分では、テストのための機能を提供しています。

「ブロックRAM・乗算器」は、論理を実現するためのリソースです。図3のように回路内全体に均一的にブロックRAM・乗算器が提供されることで、ユーザーはFPGA内での回路の位置に制限を受けることなく、演算処理とデータの保持ができます。

なお、ロジックセル内のルックアップテーブルは、ロジックの実現だけでなく小型のメモリ(4入力のLUTは16bitメモリ)として使うこともできます。従って、ブロックRAM以外に局所的にメモリを増やすことができます。この場合は、LUTを「分散型メモリ」と呼びます。

以上、説明した6つのリソースが1つのシリコンの上に組み込まれることで、FPGA内の回路配置の制限をほとんど受けることなく、希望するファンクションを実現できます。

Copyright © ITmedia, Inc. All Rights Reserved.