Pentium 4を上回る性能でASICやFPGAを駆逐:組み込み企業最前線 − アイピーフレックス −(2/2 ページ)

デジタル複合機でマス市場進出

そしていよいよ、DAPDNAは大きなマーケットに打って出ようとしている。第1弾はデジタル複合機(MFP)分野になりそうだ。

複数の入出力機能を持つMFPは、各機能でイメージ処理の負荷が大きい。一方で最近では、低コストと省スペースを売りにしたプリンタベース製品も増えており、従来とは違った開発アプローチが求められている。マーケティング部長の井手野雅明氏は「ファンクションごとに回路構成を変えられるDAPDNAなら、ハードウェアでガチガチに固めることなく、ワンチップで柔らかいシステムを作れる」と自信を見せる。

アイピーフレックスはMFP市場での展開を見据え、イメージ処理に特化した「DAPDNA-IMS」を2006年夏にもリリースする計画だ。DAPDNA-2と比較して、PEのビット幅を32bitから16bitに縮小して数を3倍に増やす(予定スペック:90nm/200〜266MHz)。「DAPDNAを評価してくれている機器メーカーからフィードバックを得て、イメージ処理に最適なPEができつつある」(萩島氏)。2006年中にもDAPDNAシリーズを搭載したMFPが製品化される見通しであるという。

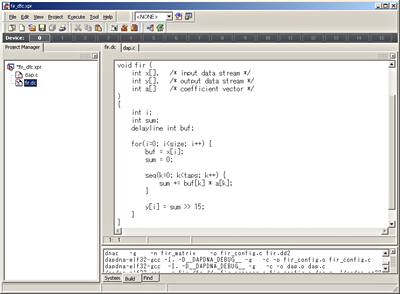

アイピーフレックスが一般市場への進出に自信を見せる背景には、力を入れてきたDAPDNAの開発環境が整ってきた面があるようだ。2004年から設計、シミュレーション、デバッグを統合した開発環境「DAPDNA-FW(フレームワーク)II」を提供する。特に開発で肝となるDNAコンフィグレーション設計に向けては、3つの手法を用意する。

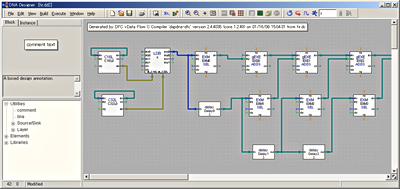

1つは、同社独自の拡張C言語である「DFC(Data Flow C)」を使ってコードを記述して、専用コンパイラにより自動的にDNAコンフィグレーションを生成するもの。特殊なHDL(Hardware Description Language)を使うFPGAと違って、ソフトウェアエンジニアでもC言語に精通していれば設計できるわけだ。もちろん、DAP実行ファイルもC言語で記述可能。もう1つは、代表的な開発ツール「MATLAB/Simulink」と連携して設計・検証する方法である。3つ目の手法は「DNAデザイナ」 と呼ぶGUIエディタを使って、ブロック図をドラッグ&ドロップしてデータ処理を記述するものだ。

井手野氏は、「最初のころのDFCは『使えない』といわれていた。ようやく最近、『これなら使えるよ』と評価してもらえるようになってきた。C言語で開発できる点はDAPDNAの大きな魅力となる」と語る。この言葉を証明するように、DAPDNA-FW IIの販売数は急増。2006年2月現在で累計212ライセンスである。

“柔らかいハード”を実現する新技術

DAPDNAが注目される理由の1つに、発展の余地が大きいことが挙げられる。前述したとおり、Pentium 4(3GHz)の50倍以上の性能を持つDAPDNA-2ですら、動作周波数は166MHzでしかない。当面、周波数アップが頭打ちになることはないだろう。トランジスタ効率もまだまだ引き上げられるという。実際、DAPDNA-IMSのそれは、DAPDNA-2の3倍近くになる見込みである。

DAPDNA性能グラフ(MIPS/MTr)。2006年夏にリリースされるDAPDNA-IMSでは、トランジスタ効率が急激に上がる見込み。年々トランジスタ効率が下がっているPentiumと比べると40〜50倍は高くなりそうだ

DAPDNA性能グラフ(MIPS/MTr)。2006年夏にリリースされるDAPDNA-IMSでは、トランジスタ効率が急激に上がる見込み。年々トランジスタ効率が下がっているPentiumと比べると40〜50倍は高くなりそうださらに、開発コード「AXION(アクシオン)」と呼ぶ新技術も開発中である。DNAのPE粒度をFPGA並みに小さくして、より“柔らかいデバイス”を実現する技術だ。「ファイングレイン(微粒子)プロセッサ」となるDAPDNAは、アプリケーションに応じてよりきめ細かく最適な回路構成へ切り替えられるわけだ。問題となる切り替え速度も、現状で17ナノ秒(59MHzの1クロック時間)を達成できているという。AXION技術を採用した「DAPDNA-3」(予定スペック:90nm/250MHz以上)を2007年にもリリースする計画。プロトタイプはすでに完成している。

萩島氏はDAPDNA-3の用途を次のように説明する。「AXION技術なら細かなビット処理も効率的に行えるので、例えばハフマン符号化の処理に向いている。いまのデジタル機器の多く、DVDレコーダからデジタルテレビ、ワイヤレス機器、OA機器までがデータ暗号化にハフマン符号化を使っているので、DAPDNAの適用範囲は一気に広がる」。

次のような活用法も考えられる。DAPDNA-3プロセッサをマルチコアで接続する場合、プロセッサ間のバスをAXION技術で動的に構成すると、必要なときに必要なだけのバス幅を確保できる。ハードウェアで固定的に最大バス幅を用意するのに比べてムダのないシステムを作れる。

さらに2009年からは、DAPDNA-3をベースにして用途別に製品を分岐していく開発ロードマップも描かれる。情報家電向けに特化した「DAPDNA-CE」(予定スペック:65nm/333MHz以上)、ワイヤレス機器向けの「DAPDNA-WL」(同:65nm/666MHz以上)、ハイエンド産業機器向けの「DAPDNA-AX」(同:65nm/1.3MHz以上)、DAPDNA-IMSを発展させた「DAPDNA-IMX」(同:65nm/250MHz以上)とラインアップを分けてゆく。

特に情報家電向けDAPDNA-CEは、国からも産業競争力強化に貢献する可能性があると注目されている。新エネルギー・産業技術総合開発機構が情報家電の高度化を目指して行う助成事業「半導体アプリケーションチッププロジェクト」で、ネット放送向けSTB(セットトップボックス)用としてDAPDNA-CEの研究開発が助成対象となった。

井手野氏は「通信と放送が融合する世界では、著作権保護やコーデック、暗号化などでそれぞれ複数の規格が使われる。受信機には全対応が迫られ、ユーザーの手に渡った後でも新規格への対応が求められてくる。そうなるといまのようにASICでハードウェアを作り込むわけにもいかず、コストと消費電力からいってプロセッサを何個も搭載することもできない。その点、DAPDNAのようなダイナミック・リコンフィギュラブル・プロセッサならワンチップで多くの規格へ柔軟に対応できる。この条件はどの情報家電にも当てはまる。デュアル、トリプルの通信モードをサポートすることが一般的になるワイヤレス機器でも同じ」と見通す。

これからもDRPが持つ柔軟性へのニーズが増し、実採用が増えることは間違いないようだ。採用実績でDRP市場をリードするアイピーフレックスにとっても、ビジネスを拡大させるチャンスは大いにあるだろう。もちろん、国内大手メーカーもDRPに力を入れてくることは確実。技術の高い海外ベンチャーも競争相手となる。ここからが本格的な勝負だ。技術力を持ちながら花開かなかった国内ベンチャー企業は数多い。

それでも萩島氏は「機器メーカーがASICやFPGAからDRPへ一斉に乗り換えるパラダイムシフトが起こるのは時間の問題だろう。そのときにも市場のリーダーであり続けられるように、今後も着実に実績を積み重ねてゆく。幸いにして、各分野のトップメーカーとも良い関係ができつつある」と自信をにじませる。

- FPGA拡大の波に乗るOKIアイディエス、運転支援で車載向け狙う

- 無線LANソリューションでInternet of Things時代の勝者となるか!?

- 設計・製造の一貫対応でFPGAソリューションを推進する

- 機器のマルウェア対策はホワイトリスト型が効く

- Androidでビジネス拡大を狙うミップスの新戦略

- アクテル、“真の”Flash FPGAでPLD市場を広げる

- メンターは組み込みソフトにコミットする

- “進化するケータイカメラ”を支えるモルフォの組み込み技術

- ドコモが認めた技術を“ケータイ以外”へ

- AUTOSAR適用の「現実解」を提供するベクターの役割

- Linux基盤「ALP」でケータイOSのエコシステムを構築

- Answers Anywhereで車載向け音声ポータルを狙う!

- ケータイ標準DBに躍り出た! Linterの歩み

- 組み込み分野へ急接近、リアルとシミュレーションをつなぐ

- ユーザーはLinuxから戻ってきた「RTOS“Nucleus”を汎用OSへ」

- Blackfin、“柔軟性”によるマルチプラットフォーム戦略で差別化

- ユーザーと育てたシミュレータで手戻り削減

- TIのDSP、ケータイの次の目標は家電&カーナビ

- 車載用半導体トップメーカーの強みとは?

- ICEメーカーによる携帯端末開発プラットフォーム

- CPLDからFPGA、ASICまでそろうアルテラ

- FPGA+Linuxで“究極のプラットフォーム”提供

- 強気のザイリンクス「2010年にはASICに追い付く」

- Opera採用の影に最強の営業ツールあり

- 意外(?)に高いWindows Embeddedの普及率

- 携帯電話OS市場を制したシンビアン、次の一手

- カーナビへの採用でT-Kernel普及が加速

- 次世代ケータイ開発を一変させるソフト基盤とは?

- Pentium 4を上回る性能でASICやFPGAを駆逐

- 年45億個の出荷を目指すアームの戦略とは

- 半導体メーカーだからできるSIソリューションを

- 組み込み分野のソフトウェア・クライシスを防ぐ

- 業界初のLinux対応ICEが成功した理由

- 「品質100%保証」を実現するCASEツールへ

- アックスの組み込みLinuxはほかと根本的に違う

- MontaVista Linuxは携帯から自動車情報系へ

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 5G通信の遅延時間1ms以下は複数端末の制御でも可能か、東芝が量子技術で道を開く

- CAN通信におけるデータ送信の仕組みとは?

- イチから全部作ってみよう(7)正しい要求仕様書の第一歩となるヒアリングの手順

- CANプロトコルを理解するための基礎知識

- 組み込みシステム向けRTOSのシェアはTRON系が約60%

- インフィニオンのSiC-MOSFETは第2世代へ、質も量も圧倒

- 【問題7】10進数を2進数に変換するプログラム

- ソニーのLPWA「ELTRES」の通信モジュールが機能追加、システムの簡素化が可能に

- テスト消化曲線とバグ発生曲線の7パターン診断

- 6Gに向けたサブテラヘルツ帯対応無線デバイス、100Gbpsの超高速伝送を実証

図2 DAPDNA開発ロードマップ。新技術「AXION」を採用したDAPDNA-3をベースに、用途別ラインアップを拡充させてゆく方針

図2 DAPDNA開発ロードマップ。新技術「AXION」を採用したDAPDNA-3をベースに、用途別ラインアップを拡充させてゆく方針 ASICやFPGAからDRPへのパラダイムシフトが起こるのは時間の問題

ASICやFPGAからDRPへのパラダイムシフトが起こるのは時間の問題