第9回 TSVを前提としたモバイルDDR:前田真一の最新実装技術あれこれ塾(3/3 ページ)

PCIバスに対し、メモリバスは、クロックの両側エッジを使って読み書きを行うDDR技術を使い、また、バス配線をできるだけ短くしたり、バスにつながるメモリの数を少なくするなどにより、どうにか並列方式で高速化を図ってきました。

将来的には、メモリバスでも直列転送にしなければならないのではないかといわれています。

しかし、新しいモバイルDDRメモリでは、バス幅を広くして、クロックスピードを遅くしようと、高速データ転送と逆の発想から規格作りをしようとしています。

JEDECのLPDDR3の次のモバイルDDRメモリの規格はWide IOと呼ばれていますが、文字通り、非常に広いビット幅で、データ転送速度を速くしようというものです。現在、最低512ビットのデータ幅が検討されています。これは、現在のモバイルDDRメモリの最大データ幅、32ビットの16倍にもなっています。

データ幅が16倍になれば、クロックスピードを1/8に遅くしてもデータ転送速度は2倍になります。

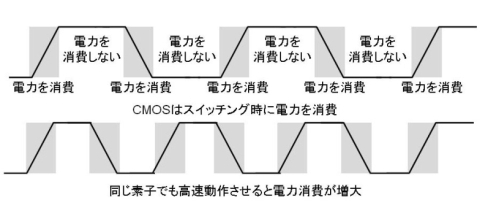

現在のIC回路で使われているCMOS回路は信号がONからOFFへ、OFFからONへ切り替わるときに電力を消費し、ONやOFFで安定している時は電力を消費しません(図6)。このため、回路の動作が高速になればなるほど、消費電力が上昇します。

このため、同じバイト数を転送する場合、バス幅を細くして高速で転送する場合に比べ、バス幅を広くして低速で転送した方が消費電力が少なくなります。もし、このような幅の広いバスが実現できるのならば、データ転送速度の高速化と、消費電力の低減が同時に実現できます。

しかし、同時に多くのビットをスイッチングするため同時スイッチング(SSO)ノイズは大きくなります。一番の問題は多くのビット数データを同期させる問題です。前にも説明しましたが、システムが高速になるに従い、複数データの同期が困難になってきたため、パラレルバス方式では高速化に限界があり、シリアルデータ転送方式になってきたわけです。

そこに、さらなるバスの高速化を図るためにデータバスのバス幅を広げることは可能なのでしょうか?

また、同時スイッチングバイト数を増やして、その深刻性が増えている同時スイッチングノイズ問題は解決できるのでしょうか?

TSVがその解決の鍵になる、というよりも、TSVの出現によって、Wide IOの考えが出てきたのです。

5. TSVとシリコンインターポーザ

Wide IOメモリはTSV(Through Silicon Via)ができてはじめて実現できるメモリです。

高速パラレルバスのデータスキュー問題は信号配線が長いほど深刻になります。これは、クロストークノイズや反射ノイズ、伝播速度の誤差によるスキューや損失による波形劣化やそれによるISIなど、基板配線に起因するスキューの問題の多くは、配線長さに依存しているからです。

このため、配線が長くなる、PCIバスはいち早くシリアル化してPCI Expressとなりましたが、DDR3やDDR4の高速メモリバスは配線をできるだけ短くすると同時にメモリやコントローラ内の回路を工夫することにより1GHz以上の高速でも8ビットや16ビットのパラレルバスを実現しています。

しかし、パラレルバスでは2.5GHzや4GHzといった、PCI Express Gen2、Gen3に匹敵する速度は非常に困難です。

これを速度は多少遅いとはいえ、現在の32ビットバスから512ビットバスへと16倍のバス幅を持たせるのは、これまでの技術の延長では不可能です。バスのビット数が増えれば、ICのピン数も増え、また、バスの配線幅も広くなります。

これは、ICパッケージの大型化と、配線長さの増大につながります。例えば、512本の基板配線を等長で配線することは不可能ではないかもしれませんが、長さを揃えるために配線は非常に長くなってしまうでしょう。しかも基板の層数はいくつになるかは想像もできません。

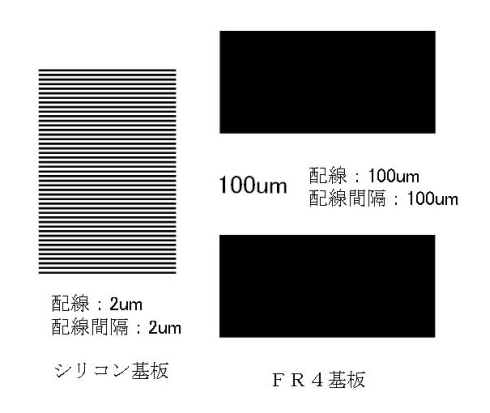

しかし、メモリとコントローラの信号接続にシリコン基板を使い、配線幅を1μm程度の細くできれば、多くの配線を非常に狭い配線領域で配線することができます(図7)。配線幅を1/100にすれば、同じ領域で100倍の配線が可能となります。

複数のメモリチップとコントローラICチップをシリコン基板を介して3次元実装すれば、配線はさらに短くなり、クロストークノイズや反射ノイズを大幅に低減できるばかりではなく、ドライバのドライブ能力を小さくすることができ、消費電力を減らし、同時スイッチングノイズを低減させることができます。

また、シリコン基板は表面が平坦で特性が安定しているため、配線特性のバラツキを小さくすることができます。絶縁層を形成する酸化膜の特性をコントロールすることにより、誘電率をコントロールすることもできます。

今日、TSVとシリコン基板は非常に期待されている技術で、学会や新技術発表での発表は数多く行われています。しかし、低コストでの大量生産となると、まだ先の技術になっています。

本命のWide IOが安価で大量に製品化されるまでは今ある技術でLPDDR3を使う。これがJEDECの方針となっています。

参考文献

(1)「Low Power Double Data Rate (LPDDR) SDRAM Standard」JESD209B FEBURARY 2010

(2)「Low Power Double Data Rate 2 (LPDDR) 」JESD209-2E APRIL 2011

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

関連記事

第8回 モバイルDDR

第8回 モバイルDDR

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第8回は、スマートフォンをはじめ、モバイル機器の高度化によって需要が拡大しているモバイルDDRメモリについて説明する。 第3回 TSVがもたらす新しいMCM

第3回 TSVがもたらす新しいMCM

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第3回は、パッケージ内でメモリチップを積層するためのキーテクノロジとして注目されている「TSV」について紹介する。 第1回 DDR4

第1回 DDR4

「実装が新しい技術の普及を左右している――」。実装技術の専門誌「エレクトロニクス実装技術」で好評連載中の前田真一氏がMONOistに登場。実装分野の最新技術を分かりやすく紹介する。第1回のテーマは、次世代メモリ「DDR4」だ。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 品質保証とは何か、その定義を改めて考える

- タイの半導体製造工場で新棟が完成、ソニーセミコンが生産力を強化

- 三菱重工が航空機エンジン部品工場を増強、内製力強化で完全一貫生産を実現

- パワー半導体の電流測定が正確に、光プローブを用いた電流波形測定用センサー

- ルネサスが甲府工場で300mmウエハーライン稼働、パワー半導体の生産能力を2倍に

- 日立産機が三菱電機 名古屋製作所の配電用変圧器事業を譲受、2026年4月に統合完了

- 工場でCO2排出量1次情報をなぜ取得すべきなのか 85%以上の削減効果も

- 誤差9割、コストを抑えるためにもCO2排出量は測った方がよい

- OTセキュリティを巡るエネルギー業界の法改正とは、変わる事業者の事故対応

- IEC 62443とは何か、工場のサイバーセキュリティ対策のカギを握る国際標準を解説