第13回 TSVが量産技術へ〜Wide I/O規格:前田真一の最新実装技術あれこれ塾(2/3 ページ)

3. 機械的仕様の概要

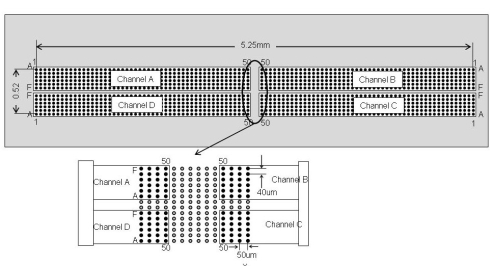

規格では、メモリチップは最大4枚になっていますが、インタフェース的にも300パッドのチャンネルと呼ばれるブロックが4チャンネル存在します。

Wide I/Oメモリでは、1チャンネルには6列50行の300パッドが40μm×50μmピッチで配置されます。

これが2×2の4チャンネル配置され、合計1200パッドとなります(図3)。

このため、パッドの占有面積は(5.25+α)×(0.52+α)mmとなります(αはパッドの径)。

メモリのチップサイズはパッドレイアウト幅の0.52mmよりは大きいので、メモリ外形はさらに大きくなるでしょうが、現在は、パッケージサイズは定義さえていません。

4. 電気的仕様の概要

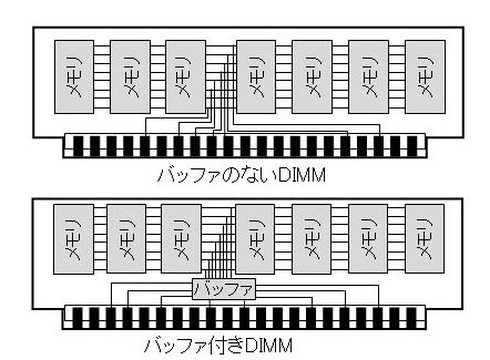

DIMMなどのように、コントローラICに複数のメモリを接続する場合には直接メモリを接続する場合とバッファを介して接続する場合があります(図4)。

JEDECの規格としては、DDR規格とかLPDDR企画などのメモリ単体の規格のほか、DIMMの規格も制定しています。DIMM規格では、バッファのあるDIMM規格とバッファのないDIMM規格を定めています。

しかし、今回のWide I/Oメモリでは部品としては、必ずバッファチップを必要とし、メモリチップをその上に3D実装する構造をとっています。このため、Wide I/Oの電気特性規格の多くはバッファチップの電気特性になっています。

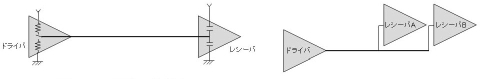

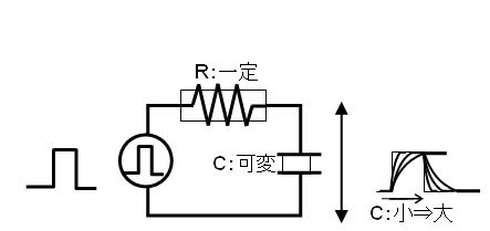

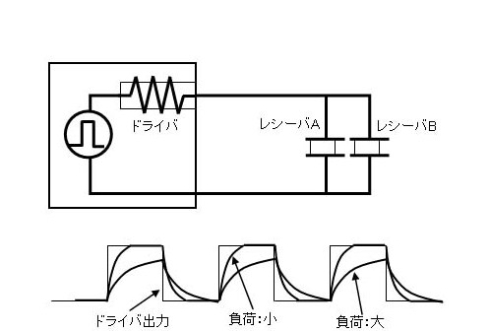

メモリインタフェースのCMOS回路では、レシーバの入力容量の大きさが重要です。CMOS回路では、レシーバの入力インピーダンスは高いので、ドライバの出力インピーダンスとレシーバの入力容量で積分回路を形成します(図5)。

図6の回路のCで示される、レシーバの入力容量が大きいと、信号波形が鈍り、信号の高速伝送ができなくなります(図6)。

もし、バッファがなく3D実装された複数のメモリチップがコントローラICに直接、接続された場合、チップの数が増えるほど入力容量が並列接続され、信号が低速になってしまいます(図7)。

このため、複数のメモリチップを3D実装する場合には、複数のメモリチップを直接基板配線に接続しないで、低容量のバッファを介して基板配線に接続する必要があります。

メモリパッケージ内のバッファとメモリチップ間の接続では配線が非常に短いため、複数のチップを接続して容量が大きくなっても、信号の高速伝送が可能です。

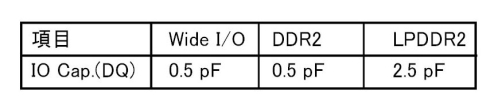

バッファがあるためWide I/Oの規格では、メモリチップが1つだけ使われているDDR2規格やLPDDR2規格と同じ入力容量になっています(表1)。

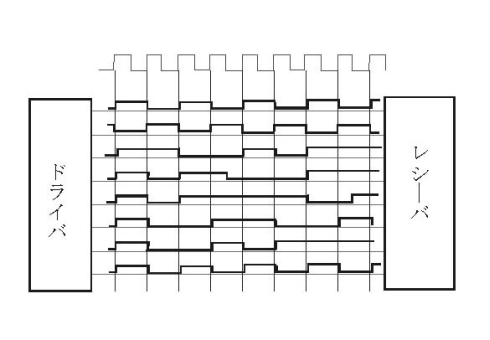

メモリバスのような並列データ転送方式ではデータ間のタイミングの同期が最も重要です(図8)。Wide I/Oメモリではデータ転送速度を遅くして同期時間に余裕をもたせました。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- PLCレスで協働ロボットの外部軸を制御、自動化システム構築の工数削減

- ラズパイの電源を入れてみた

- ハノーバーメッセが開幕、AIや水素など「競争力ある持続可能な産業」の最新技術

- 品質保証とは何か、その定義を改めて考える

- RYODENらが生成AIの事業応用で協業、現場映像と設備データの融合も目指す

- IEC 62443とは何か、工場のサイバーセキュリティ対策のカギを握る国際標準を解説

- HOYA、生産ラインや受注システムのシステム障害からほぼ復旧

- サーバなど向け、高風量かつ高静圧ながら連続運転10万時間の長寿命な冷却ファン

- マレーシアで半導体ウエハーバンピングの受託加工向け製造装置増設

- タイの半導体製造工場で新棟が完成、ソニーセミコンが生産力を強化

図4 バッファのある場合と無い場合

図4 バッファのある場合と無い場合

図6 積分回路

図6 積分回路 図7 負荷を並列接続すると信号は遅くなる

図7 負荷を並列接続すると信号は遅くなる 表1 DDRメモリの入力容量規格

表1 DDRメモリの入力容量規格 図8 並列バスでは信号の同期が重要

図8 並列バスでは信号の同期が重要