第38回 IBISの新しい傾向:前田真一の最新実装技術あれこれ塾(5/5 ページ)

5.IBIS Package Modelの問題

IBISモデルを使った波形解析では、常に解析結果の精度が問題になります。

特に、高速信号ではIBISモデルでは精度が悪いので、SPICEモデルを使わなくてはいけないのではないかとの質問が出されます。

これには、ある程度の真実があります。

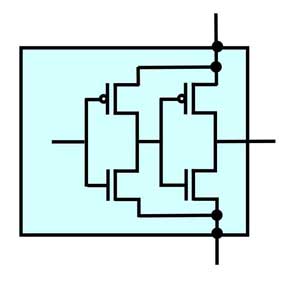

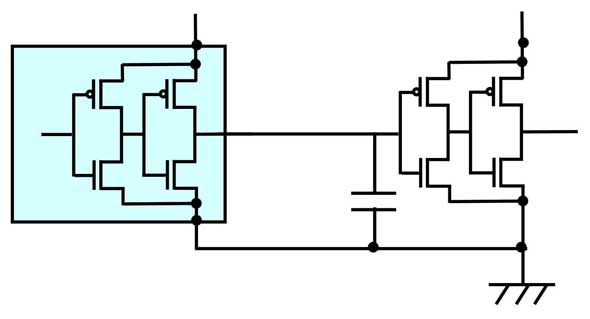

SPICEモデルは電子回路そのものなので、どのような周波数の回路にも対応しています(図6)。

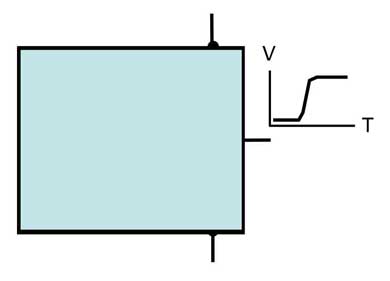

それに対して、IBISモデルは回路をブラックボックスとして扱い、ブラックボックスからの入出力の特性だけを定義しています(図7)。

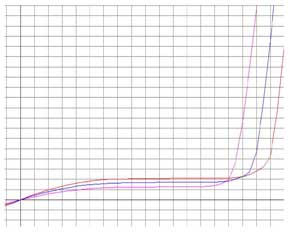

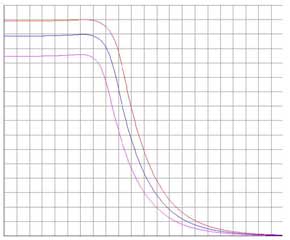

これが、IBISモデル定義のI-V特性、V-t特性です(図8)。

実際のIBISモデルでは、SPICEモデルを使い、SPICEシミュレータで解析してI-V特性、V-t特性を抽出しています。この意味ではIBISモデルもSPICEモデルから作成しているので、精度的には問題ないともいえます。

しかし、IBISのI-V特性とV-t特性は、回路に接続する負荷や電源条件を決められた条件に設定して特性を解析しています。負荷や電源電圧が特性を抽出した条件と異なる場合は、条件に合わせて特性を手直ししてやる必要があります。このため、IBISモデルでは、特性を抽出した条件を定義したり、V-t特性では、条件を変化させた複数の特性をモデルに記述できるようにしています。しかし、条件に合わせて特性を変更させることはシミュレータに任せています。

このため、シミュレータによって、同じIBISモデルを使って解析しても、結果が異なることがあります。SPICEモデルでは回路を直接モデル化しているので、負荷や電源の条件が変化しても、負荷回路など、外部の回路を変化させれば、変化に応じた解析がそのまま実行されそれに応じた結果がそのまま出力されます(図9)。

これが「IBISモデルの精度が悪い」といわれる原因の1つです。IBISモデルの精度が問題となるもう1つの原因がPackageモデルと呼ばれる部分の定義の問題です。

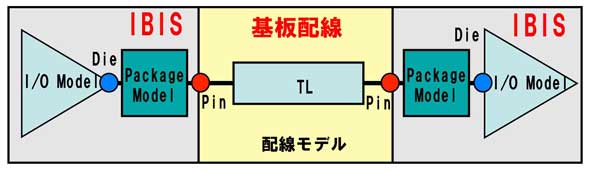

IBISモデルはICのドライバ、レシーバのモデルです。

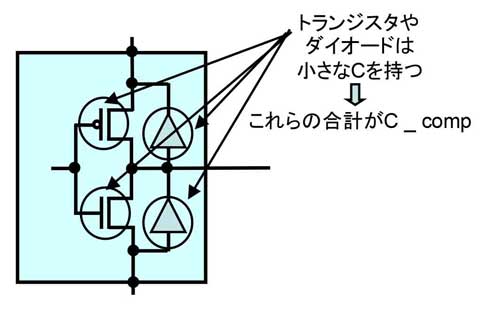

ICチップ内のドライバ、レジーバ・モデルは「IOモデル」と呼ばれ、これまでに出てきたI-V特性、V-t特性で定義されます。この他にCMOS素子では、ドライバ、レシーバがもっている小さな浮遊容量が波形に大きな影響を及ぼすので、C_compと呼ばれる定義で、規定されています(図10)。

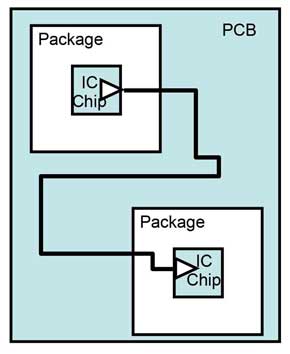

ICチップのドライバ、レジーバが直接基板に接続されているわけではなく、基板の部品パッドの間にはパッケージの配線が存在します(図11)。

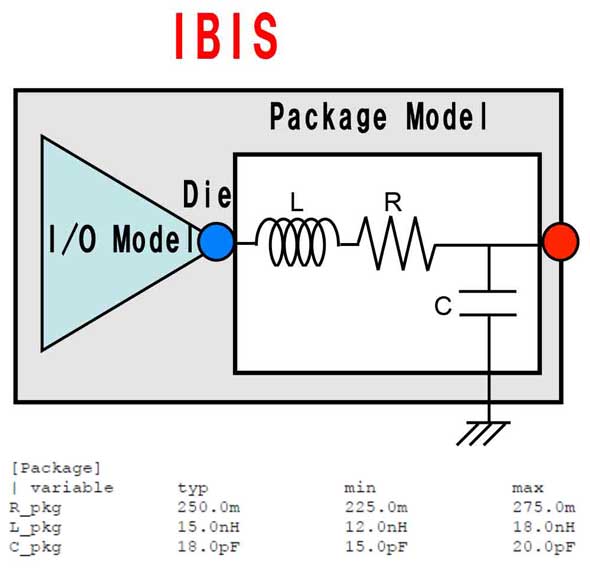

このパッケージ配線の特性定義は「Packageモデル」と呼ばれ、IBISモデルはIOモデルとPackageモデルの2つのモデル定義から成り立っています(図12)。

IBIS SummitでのKen Willis氏のプレゼン(参考文献2)にもありますが、最初にIBISモデル規格を考えた時は信号速度は33MHzで、パッケージ内配線もリードフレーム(図13)など、短く単純なものが多い時代でした。

信号速度に比べ、パッケージ内配線は短く、伝送線路ではなくR、L、Cの集中定数回路として考えるべきでした。

そのため、IBISモデルのPackageモデルの基本定義はR、L、Cが1つずつ(1段)の定義になっています(図14)。

信号の高速化とパッケージ内配線の複雑化にしたがい、パッケージ内配線の特性も伝送線路として解析する必要があるようになりました。また、その後クローズアップされてきた PI(Power Integrity)解析のためにPackage内の電源・グランド配線情報も必要となってきました。

このため、IBIS規格の次のバージョンではPackageモデルの定義を改善しようということで、今回のIBIS Summitでは各社からPackageモデル改善案の提案が多くなったのです。

引用・参考資料

- 1)An Advanced Behavioral Buffer Model with Over-Clocking Solution、Yingxin Sun、Joy Li、Joshua Luo、Cadence Design Systems、2014、IBIS Summit - DesignCon

- 2)RANTINGS OF AN IBIS MINIMALIST、Ken Willis、Cadence Design Systems、2014、IBIS Summit - DesignCon

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

関連記事

- ≫前田真一の最新実装技術あれこれ塾

「社名がマイクロンになってもエルピーダの火は消えない」、坂本社長が退任の弁

「社名がマイクロンになってもエルピーダの火は消えない」、坂本社長が退任の弁

米国の半導体メモリ大手マイクロンは、国内唯一のDRAMメーカーだったエルピーダメモリの買収を完了したと発表した。2013年末までに、エルピーダの社名はマイクロン・メモリー・ジャパンに変更される。社長を退任する坂本幸雄氏は、「社名は変わるが、エルピーダの火が消えるわけではない」と述べた。 第2回 IBISの新動向

第2回 IBISの新動向

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第2回テーマは「IBIS」。最近のIBISが決めた標準化とIBIS-ISSについて紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 品質保証とは何か、その定義を改めて考える

- 日立産機が三菱電機 名古屋製作所の配電用変圧器事業を譲受、2026年4月に統合完了

- 信越化学が群馬県伊勢崎市に半導体露光材料の新工場建設、約830億円を投資

- 三菱重工が航空機エンジン部品工場を増強、内製力強化で完全一貫生産を実現

- 工場でCO2排出量1次情報をなぜ取得すべきなのか 85%以上の削減効果も

- 変わらないものを持ち続けることも尊い

- AIを活用した設備異常検知システム、正常データのみで閾値まで提案

- ニコンが補修用途向け金属3Dプリンタ発売へ、加工パスは3Dスキャナーで自動生成

- 工場のスマート化で高まるサイバーリスク、経産省が対策の要点など公開

- デジタルトリプレットとは何か デジタル化で一周回って重要になる現場力の必要性

図6:SPICE Model

図6:SPICE Model 図7:ブラックボックス

図7:ブラックボックス

図8:I-V特性、V-t特性

図8:I-V特性、V-t特性 図9:SPICE回路の負荷接続

図9:SPICE回路の負荷接続 図10:C_ comp

図10:C_ comp 図11:チップと基板の間の接続

図11:チップと基板の間の接続 図12:I/OモデルとPackageモデル

図12:I/OモデルとPackageモデル 図13:リードフレーム

図13:リードフレーム 図14:R、L、C、1段定義(IBIS Version 6 Specification)

図14:R、L、C、1段定義(IBIS Version 6 Specification)