ルネサスの自動運転システム向けSoC、ISO26262のASIL Bに対応する機能を実装:ISO26262(2/2 ページ)

処理を中断せずに自己テストするには

新開発のランタイムセルフテスト機構は自己テストを機能ブロック別に、あるいは1種類の自己テストを複数回に分けて実施できるようにした。この結果、プログラムの実行を中断する必要がなく、処理中断時間が発生しても2ms以下に抑えることが可能になった。

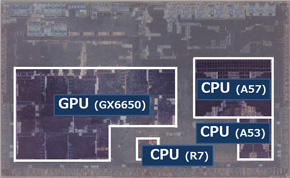

具体的には、CPUやGPUの機能ブロックごとに自己テスト用のハードウェアを搭載し、さらに複数の自己テスト用ハードウェアを統合制御するコントローラーも実装した。この設計により、複数のCPUで構成するCPUクラスタのうち、特定のCPUのみで自己テストを実行して残りのCPUでは処理を継続できる。また、特定のCPUで実施する自己テストを複数回に分けることで、処理中断時間を最小化する。

ハードウェアによる自己テストは、ソフトウェアのみによる自己診断と比較してテスト時間が短縮できるメリットがある。また、論理回路を冗長化せずにハードウェアの故障を検出できるため、大規模回路での利用に適している。

SoCにありがちな故障を回避する

R-Car H3は、情報の処理速度を急激に高めた場合に起こる、瞬間的な電圧の降下に伴うハードウェアの故障を回避する機能も備える。この電圧降下は、SoCの回路の動作周波数や活性化率の変化量が大きいほど顕著になる。従来は電圧マージンを設ける設計で対応できたが、16nmプロセスを採用して微細化が進んだR-Car H3では、電源の低電圧化や周波数増加による電流変化量の拡大のため電圧マージンを設ける設計が難しい。

電圧降下に伴うハードウェアの故障を回避するため、電圧降下を事前に検知して回路が活性化しすぎないように制御する技術を開発した。この技術は3つの機構で構成している。

1つ目は、高速動作が可能な電圧検知機構だ。電圧差によって伝搬時間が変化する可変遅延回路と基準クロックとの時間差をデジタル値に変換するTime-to-Digital変換機を組み合わせている。電圧のゆるやかな低下による処理の遅延時間と、基準クロックとの差を測るもので、CPUクロックと同じ2GHzで動作する。

2つ目の電圧降下予測機構は、電圧検知機構で得た電圧の情報をもとに4サイクル先の電圧値を予測する。あらかじめ設定した閾(しきい)値を下回る場合は、3つ目の機構である高機能クロック制御機構が制御対象へのクロック供給を停止し、回路の過度な活性化を防ぐ。また、クロックの供給は低い周波数から徐々に回復させることで、クロックの供給再開に伴う電圧降下も防ぐ。

この機構により、電圧降下が原因となるハードウェア障害を抑制し、安全性を高められる。

関連記事

ルネサスの第3世代「R-Car」が半自動運転を可能にする

ルネサスの第3世代「R-Car」が半自動運転を可能にする

ルネサス エレクトロニクスは、車載情報機器向けSoCの第3世代「R-Car H3」のサンプル出荷を開始した。半自動運転に相当するレベル3の自動運転システム向けに、HMIの描画性能と情報処理性能を進化させた。 ルネサスが語る、クルマを安全に制御する車載マイコンの“技術の四隅”

ルネサスが語る、クルマを安全に制御する車載マイコンの“技術の四隅”

ルネサス エレクトロニクスが、自動運転を視野に入れた運転支援システム向けに開発した車載マイコン「RH850/P1x-Cシリーズ」は、同社が「車載マイコンの技術の四隅」と呼ぶ、クルマを安全に制御する4つの技術課題をクリアしている。 ルネサスがRXファミリ向けの機能安全搭載支援ソリューションを発表

ルネサスがRXファミリ向けの機能安全搭載支援ソリューションを発表

ルネサス エレクトロニクスは、32ビットマイコン「RX631」「RX63N」を搭載する機器に機能安全システムを組み込むためのマニュアルやソフトウェアの提供を2014年2月から開始する。主に産業機器での機能安全対応を支援する。 機能安全対応の走行モーター用マイコン、外付けのレゾルバ用変換器ICが不要に

機能安全対応の走行モーター用マイコン、外付けのレゾルバ用変換器ICが不要に

ルネサスの「V850E2/PJ4-E」は、自動車向け機能安全規格ISO 26262に対応する走行モーター制御用マイコンだ。従来は外付けしていたレゾルバ用変換器ICが不要になる機能も搭載している。

Copyright © ITmedia, Inc. All Rights Reserved.