第52回 DDR4の市場と技術:前田真一の最新実装技術あれこれ塾(3/4 ページ)

3.DDR4の同期技術

DDR4メモリは当初、データ転送速度1600M〜3200Mbpsをカバーする規格として、立案されました。これは、クロック周波数としては800MHzから1600MHzです。

しかしその後、DDR3は1066MHzまで高速化を図ってきました。同様に、DDR4も現在、規格にはありませんが、2400MHzや2666MHzのクロックで動作するメモリが作成されています。今後、DDR4メモリもDDR3メモリと同様にクロックが3.2GHz程度まで高速化が図られてくるものと思われます。

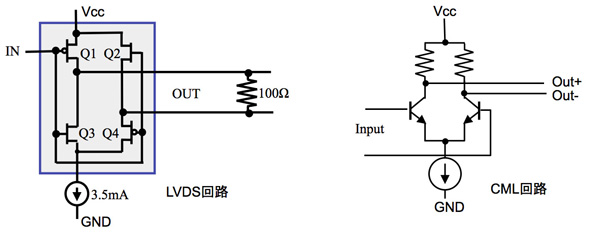

最大8ビットの同期信号を1GHz以上のクロック速度で、DDR技術で同期させるのは非常に大変なことです。PCI ExpressやUSBに代表されるシリアルデータ転送方式では、LVDSやCMLといった差動信号素子を使います(図2)。

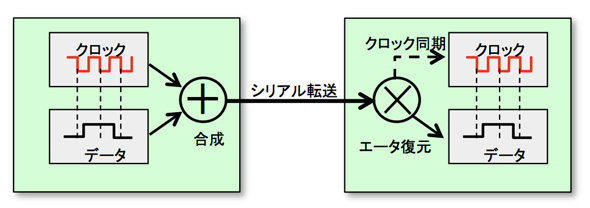

この差動伝送と、クロック信号とデータを合成して同時に送ることにより、データとクロックの同期ずれの問題を解決し、GHz以上の高速転送が可能となりました(図3)。

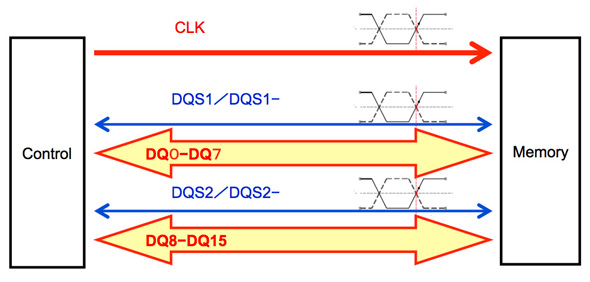

しかし、DDRメモリはシングル信号転送のCMOS回路を使い、同期信号と多くのデータ信号を並列に伝送します(図4)。

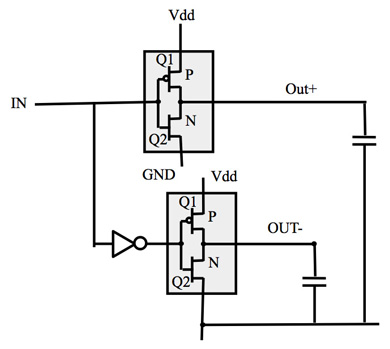

CMOS回路では信号はHighかLowのどちらかしか出力できません。CMOS回路で差動信号と言っているのは、2つのCMOSドライバを使って常に逆向きの信号を出力するようにしているものです(図5)。

DDR転送方式ではデータ転送速度はクロック周波数の2倍となります。1GHzのクロックでは1周期は1nSで、データの転送サイクルは500pSしかありません。2GHzのクロックでは、250pSの間に最大8ビットのデータ全てを、High/Lowに安定させる必要があります。

IC素子は特性にばらつきがあり、出力信号がHigh/Lowに安定するまでの時間に多少の誤差があります。

また、入力側でも信号がHighかLowかを判定するスレッショルド電圧に素子ごとのばらつきがあります。スレッショルド電圧が異なれば、HighかLowかを判定する時間にばらつきが出ます。

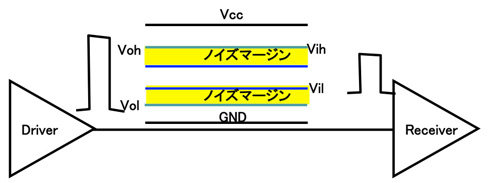

スレッショルド電圧では、ドライバがHigh/Lowの電圧を保証するVoh電圧とVol電圧、レシーバがHigh/Lowを認識するVoh電圧とVil電圧が定められています。そして、VohとVih、VolとVilの差がノイズマージンになります(図6)。

DDRメモリのような高速同期式伝送システムではタイミング方向にもノイズマージンと同様にタイミングマージンがあります。

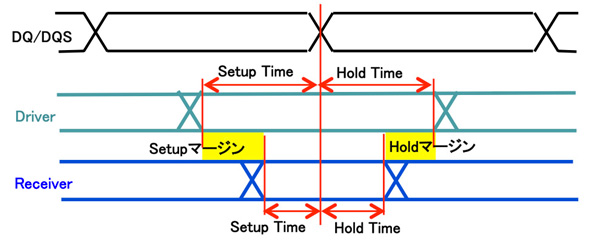

タイミングの基準に対して、ドライバはどれだけ前に信号のHigh/Lowを安定して出力できるかという時間の保証値があります。これをSetup Timeと呼びます。同様に、基準からどれだけ後まで信号のHigh/Lowを安定させておけるかの時間の保証値があり、これをHold Timeとよびます。

同様にレシーバ側にもSetup TimeとHold Timeがあります。これは、レシーバがHigt/Lowを認識するためには、基準時間からどれだけ前(Setup Time)からどれだけ後(Hold Time)までデータが安定していなければデータを正しく読み込めないという時間です。

このドライバのSetup、Hold時間とレシーバのSetup、Hold時間の差がタイミングマージンとなります(図7)。

このSetup、Holdタイムはタイミングの基準時間からの時間です。

クロック(CLK)は基準時間になりますが、データ(DQn)はバイトごとにクロックとは別のデータ同期信号(DQX)に同期して転送されます。

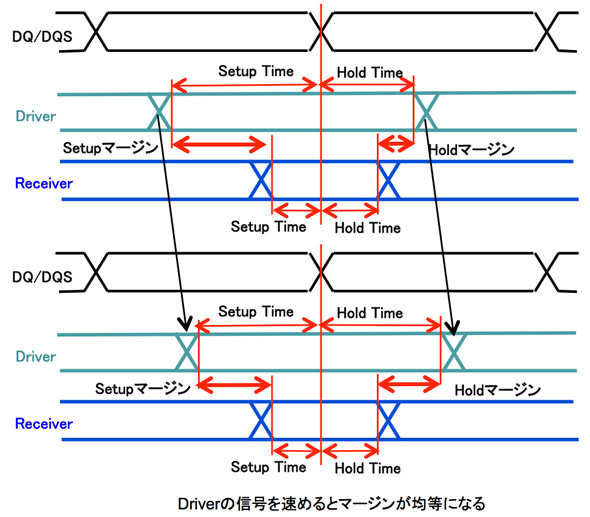

当然、CLKとDQX信号、DQX信号とDXn信号の間にはタイミングずれに対する厳しい許容誤差範囲があります。しかし、許容誤差範囲内でも、ずれがどちらかに偏るとSetup側やHold側のマージンが極端に大きく、反対側のマージンが小さくなってしまうことがあります。

DDR3とDDR4では、システム起動時にSetpuマージンとHoldマージンが均等になるようにCLKとDQXのタイミングを調整する機能があります。これをレベリング機能と呼びます(図8)。

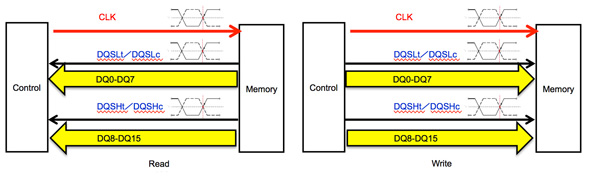

クロック信号はホスト(CPUやASIC)側からDDRメモリに出力します。それに対してデータ(DQn)やデータ同期信号(DQX)はデータ書き込み時にはホストからメモリへ、データ読み出し時にはメモリからホストへ出力されます(図9)。

データ書き込み時のマージン調整をライトレベリング(Write Leveling)、データ読み込み時のレベリングをリードレベリング(Read Leveling)と呼びます。この2つのレベリングは異なる機能です。また、信号転送速度の向上に従い、データのRead/Writeが困難になる対策として、データにはCRCと呼ばれる、データの誤り訂正機能を追加しました。

同様に、アドレス信号やコマンド信号にはパリティビットによる誤り検出機能を付加しました。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 品質保証とは何か、その定義を改めて考える

- 三菱重工が航空機エンジン部品工場を増強、内製力強化で完全一貫生産を実現

- タイの半導体製造工場で新棟が完成、ソニーセミコンが生産力を強化

- ルネサスが甲府工場で300mmウエハーライン稼働、パワー半導体の生産能力を2倍に

- パワー半導体の電流測定が正確に、光プローブを用いた電流波形測定用センサー

- 日立産機が三菱電機 名古屋製作所の配電用変圧器事業を譲受、2026年4月に統合完了

- 工場でCO2排出量1次情報をなぜ取得すべきなのか 85%以上の削減効果も

- 誤差9割、コストを抑えるためにもCO2排出量は測った方がよい

- OTセキュリティを巡るエネルギー業界の法改正とは、変わる事業者の事故対応

- IEC 62443とは何か、工場のサイバーセキュリティ対策のカギを握る国際標準を解説

図2:差動出力ドライバ

図2:差動出力ドライバ 図3:シリアル伝送の埋め込みクロック

図3:シリアル伝送の埋め込みクロック 図4:並列伝送

図4:並列伝送 図5:CMOSの差動出力

図5:CMOSの差動出力 図6:スレッショルド電圧とノイズマージン

図6:スレッショルド電圧とノイズマージン 図7:タイミングマージン

図7:タイミングマージン 図8:レベリング機能

図8:レベリング機能 図9:ReadとWrite

図9:ReadとWrite