「MAX 10 NEEK」に搭載されたDDR3メモリを使う:MAX 10 FPGAで学ぶFPGA開発入門(10)(6/6 ページ)

» 2016年05月19日 07時00分 公開

[大原 雄介,MONOist]

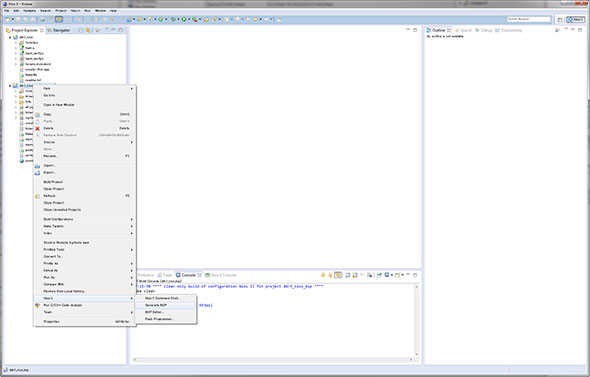

2つのProjectの両方とも「Clean Project」を指定してクリアにした後で、ddr3_nios_bspのプロジェクトを右クリック、“ Nios II ”→“ Generate BSP”を指定してBSPの再構築を行う(Photo24)。

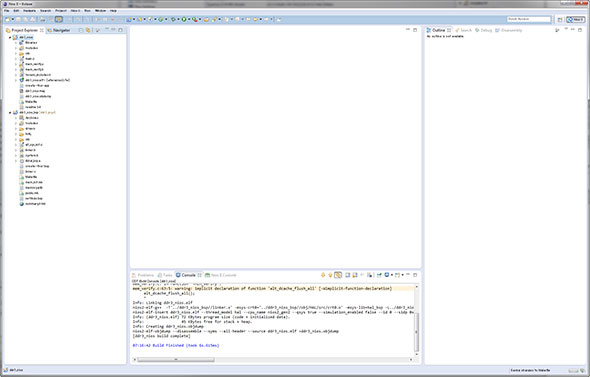

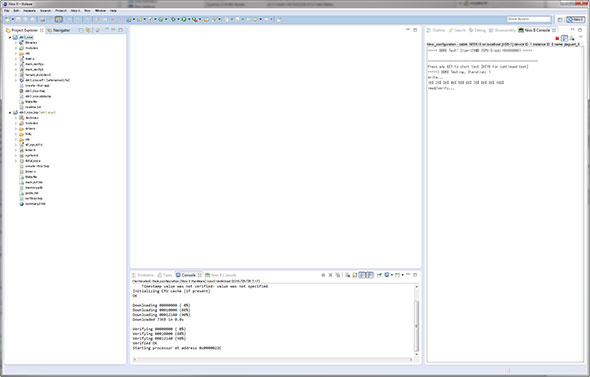

これが済んだらまずddr3_nios_bspをビルドし、次にddr3_niosをビルドする。完成するとWarningが1つ出るが、これは無問題(Photo25)。Run Configurationで設定を行ったら実行する。問題なければこんな具合に実行が始まる(Photo26)。問題が無ければ、WriteとRead/Verifyが21秒で完了するはずだ。

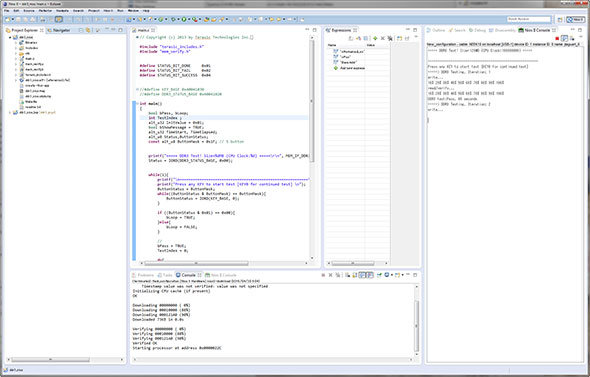

さて、ここまではサンプルにある「ddr3_test」そのままである。これをNiosII/eに切り替えるとどの位遅くなるか、をちょっと試してみた。

手順は簡単で、QSYSのプロパティ画面(先のPhoto14だ)でNios II/eに切り替え、QSYSでGenerate HDL → Quartus IIでコンパイル → Programmerで書き込み(今度は_time_limitedの付かないddr3_nios.sofを指定する) → EclipseでBSPの生成 → プロジェクト再構築 → 実行、という流れである。

結果はご覧の通り(Photo27)で、60秒とNios II/fに比べて3倍近い時間がかかっている。次回はこのあたりをもう少し試してみたい。

関連記事

「MAX 10 NEEK」へソフトコアCPUを組み込む

「MAX 10 NEEK」へソフトコアCPUを組み込む

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。 周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。 FPGAのソフトコアCPUをベンチマークで測定する

FPGAのソフトコアCPUをベンチマークで測定する

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。 FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 組み込みシステム向けRTOSのシェアはTRON系が約60%

- イチから全部作ってみよう(7)正しい要求仕様書の第一歩となるヒアリングの手順

- 5G通信の遅延時間1ms以下は複数端末の制御でも可能か、東芝が量子技術で道を開く

- CAN通信におけるデータ送信の仕組みとは?

- インフィニオンのSiC-MOSFETは第2世代へ、質も量も圧倒

- CANプロトコルを理解するための基礎知識

- 景気減速でソフト開発の脆弱性対応が後手に? SBOM整備の取り組みも足踏みか

- 低価格FPGAでも文字認識AIの学習は可能なのか

- 【問題7】10進数を2進数に変換するプログラム

- スバルが次世代「EyeSight」に採用、AMDの第2世代「Versal AI Edge」