日立がCMOSアニーリングマシンを披露「最大の課題はイジングモデルへの変換」:人工知能ニュース

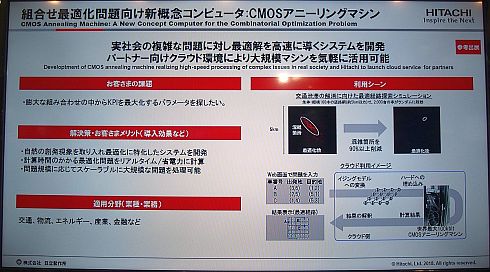

日立製作所は、プライベートイベント「Hitachi Social Innovation Forum 2018 TOKYO」において、組み合わせ最適化問題に向くコンピュータ技術「CMOSアニーリングマシン」を披露した。

日立製作所は、プライベートイベント「Hitachi Social Innovation Forum 2018 TOKYO」(2018年10月18〜19日)において、組み合わせ最適化問題に向くコンピュータ技術「CMOSアニーリングマシン」を披露した。

組み合わせ最適化問題とは、複数パラメータの組み合わせの中から、目標値が最も高くなる組み合わせを可能な限り短時間で選び出すことを目的とする問題のことだ。「巡回セールスマン問題」などが代表的だが、さまざまな要素が絡み合う実社会の複雑な問題を解決することも組み合わせ最適化問題となる。しかし、実用的な時間内で答えを出すには、膨大な計算量が必要になる。

この組み合わせ最適化問題を短時間で解くのに、最適なコンピューティング技術として注目されているのが量子アニーリングマシンだ。カナダのD-Wave Systemsなどが実用化しているが、極めて高価なことが課題になっている。

一方、日立製作所が開発したCMOSアニーリングマシンは、現行のCMOS半導体回路を用いつつ、量子アニーリングマシンと同様に、組み合わせ最適化問題を高速に処理できるとする。2018年6月には、CMOSアニーリングマシンの回路を実装したFPGAボードを25枚接続することで10万2400パラメータの問題に対応できることを示した。このCMOSアニーリングマシンを使えば、5km四方に広がる縦横160本ずつの道路から成る道路網を2000台の車両が移動する都市交通最適化シミュレーションにおいて、最短経路探索を数m秒で処理できた。

同年9月からは、同社内に設置したCMOSアニーリングマシンの計算処理能力を、クラウド型計算サービス「Annealing Cloud Web」として無償提供を始めている。

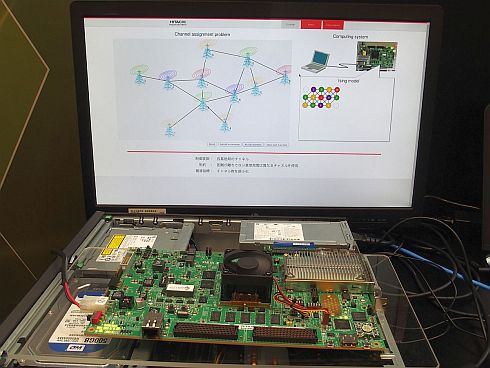

展示では、CMOSアニーリングマシンの回路を組み込んだハイエンドFPGA(ザイリンクスの「Vertex Ultrascale」)のボードを用いて、携帯電話基地局のチャネル割り当ての最適化を行って見せた。「このFPGAボード1枚で、約4000のイジングモデルのスピン数に対応している。FPGAボードを並列接続することで計算能力を高められるし、クラウドサービスの活用で気軽に利用できるようになる。ただし、量子アニーリングマシンであれ、CMOSアニーリングマシンであれ、イジングモデルへの変換が最も大きな課題になっている。今後はその解決が重要になるのではないか」(日立製作所の説明員)としている。

関連記事

量子コンピュータでなぜAIは進化するのか、全ての鍵は「最適化問題」

量子コンピュータでなぜAIは進化するのか、全ての鍵は「最適化問題」

「CEATEC JAPAN 2017」の自動運転技術に関するカンファレンスで、東北大学大学院 准教授の大関真之氏が登壇し、「量子アニーリングが拓く機械学習と計算技術の新時代」をテーマに講演を行った。 「組み合わせ最適化」が高速に、計算サービスを無償提供

「組み合わせ最適化」が高速に、計算サービスを無償提供

日立製作所は、「組み合わせ最適化問題」に特化したアニーリングマシンを活用し、クラウド型計算サービス「Annealing Cloud Web」の無償提供を開始した。サービスの利用者は、組み合わせ最適化問題の計算処理を効率的に実行可能になる。 パラメータ設定なしで組み合わせ最適化問題を解く技術を開発

パラメータ設定なしで組み合わせ最適化問題を解く技術を開発

富士通研究所は、組み合わせ最適化問題を高速に解くための計算機アーキテクチャ「デジタルアニーラ」を適用する際に、複雑なパラメータ設定なしで問題を解くことができる技術を開発した。 富士通が量子コンピュータ超える新AI技術、グラフ構造データへの深層学習適用も

富士通が量子コンピュータ超える新AI技術、グラフ構造データへの深層学習適用も

富士通研究所が人工知能(AI)技術の最新成果を発表。「量子コンピュータを実用性で超える新アーキテクチャを開発」と「人やモノのつながりを表すグラフデータから新たな知見を導く新技術『Deep Tensor』を開発」の2件である。 世界を変えるAI技術「ディープラーニング」が製造業にもたらすインパクト

世界を変えるAI技術「ディープラーニング」が製造業にもたらすインパクト

人工知能やディープラーニングといった言葉が注目を集めていますが、それはITの世界だけにとどまるものではなく、製造業においても導入・検討されています。製造業にとって人工知能やディープラーニングがどのようなインパクトをもたらすか、解説します。 製造現場で量子アニーリングを使うのに必要な“遊び心”と“親心”

製造現場で量子アニーリングを使うのに必要な“遊び心”と“親心”

少し違いますが、ジョブズとウォズニアックの関係性でしょうか。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 5G通信の遅延時間1ms以下は複数端末の制御でも可能か、東芝が量子技術で道を開く

- CAN通信におけるデータ送信の仕組みとは?

- イチから全部作ってみよう(7)正しい要求仕様書の第一歩となるヒアリングの手順

- CANプロトコルを理解するための基礎知識

- 組み込みシステム向けRTOSのシェアはTRON系が約60%

- インフィニオンのSiC-MOSFETは第2世代へ、質も量も圧倒

- 【問題7】10進数を2進数に変換するプログラム

- 景気減速でソフト開発の脆弱性対応が後手に? SBOM整備の取り組みも足踏みか

- テスト消化曲線とバグ発生曲線の7パターン診断

- 6Gに向けたサブテラヘルツ帯対応無線デバイス、100Gbpsの超高速伝送を実証