Intel、10nmプロセス世代FPGA「Agilex」を発表――アーキも一新:組み込み開発ニュース(1/2 ページ)

米Intelは2019年4月2日(現地時間)、同社の10nmプロセス技術を採用したFPGAファミリー「Agilex(アジレックス)」を発表した。同社は現在展開している「Stratix」や「Aria」「MAX 10」などの全FPGAブランドをAgilexブランドに統一する方針だ。

米Intelは2019年4月2日(現地時間)、同社の10nmプロセス技術を採用したFPGAファミリー「Agilex(アジレックス)」を発表した。同社は現在展開している「Stratix」や「Aria」「MAX 10」などの全FPGAブランドをAgilexブランドに統一する方針で、同年第3四半期にエンジニアリングサンプルの提供を開始する予定だ。

同社プログラマブル・ソリューションズ事業本部チーフプロダクトマーケティングオフィサーを務めるPatrick Dorsey(パトリック・ドーシー)氏は、「FPGAビジネスに20年携わってきたが、その中でもAgilexは最も素晴らしい製品だ。高性能なコンピューティングエンジンであり、エッジからクラウドまで“Any-to-Any”に対応するインテグレーションを提供する」と同製品について述べるとともに、ブランド名の由来がAgility(機敏さ)とFlexibility(柔軟さ)の造語であることを明かした。

アーキテクチャも刷新、新インターコネクト規格「CXL」に対応

DSP性能が最大で40TFLOPS(FP16演算時)に達するAgilexファミリーでは、10nmプロセスに加えて第2世代の「HyperFlex」FPGAアーキテクチャを新たに採用した。これにより従来製品で最も高性能のStratix 10と比べて、最大40%の高速化を実現しつつ40%の消費電力低減も両立している。

また、足回り面でも改良を積み重ねた。DDR5 SDRAMやHBM(High Bandwidth Memory)、そして同社の3D XPoint技術を用いた「Optane DC Persistent Memory」といった各種メモリに対応した他、最大112Gビット/秒(Gbps)のトランシーバを搭載。インターコネクトではPCI Express(PCIe) Gen 5や新規格の「Compute Express Link(CXL)」をサポートする。

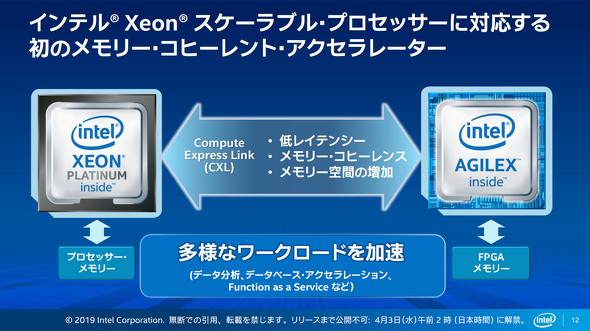

CXLは2019年3月に発表されたCPUと各種デバイスをつなぐ、主にデータセンターでの活用を想定したオープン規格。同規格ではPCIe Gen 5の物理層を活用しつつも、I/Oやメモリプロトコル、コヒーレンシインタフェースを改良、追加したものとなる。同規格を利用することによりCPUとデバイス間でメモリとキャッシュのコヒーレンシを維持できるため、互いのメモリ空間でリソースの共有や低遅延なデータアクセスといった恩恵が受けられる。AgilexはCXLに対応した業界初(同社調べ)のFPGAとなるが、CPU側もXeon Scalable Processorを含む今後登場するIntel製プロセッサで対応する方針だ。

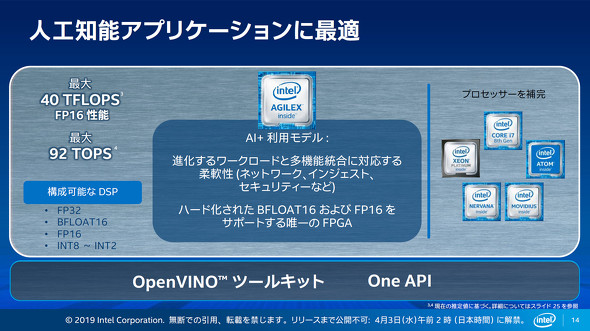

昨今注目を集めるAI(人工知能)のワークロードに対してもAgilexでは性能強化を施し、Dorsey氏は「AIアクセラレータとしても最適」なFPGAと自信を見せる。AgilexではFP32やFP16といったIEEE 754で定められた浮動小数点形式の他、ニューラルネットワークの演算精度として用いられるbfloat16(指数部8ビット、仮数部7ビットの浮動小数点形式)、INT8からINT2までの整数形式に対応するDSPを構成できる。「bfloat16に対応する初めてのFPGAであるとともに、AIワークロードに対してFPGAでトップの性能を持つ」(Dorsey氏)とし、最大で92TOPSの演算性能を発揮するという。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 5G通信の遅延時間1ms以下は複数端末の制御でも可能か、東芝が量子技術で道を開く

- CAN通信におけるデータ送信の仕組みとは?

- ソニーのLPWA「ELTRES」の通信モジュールが機能追加、システムの簡素化が可能に

- CANプロトコルを理解するための基礎知識

- イチから全部作ってみよう(7)正しい要求仕様書の第一歩となるヒアリングの手順

- 【問題7】10進数を2進数に変換するプログラム

- テスト消化曲線とバグ発生曲線の7パターン診断

- 組み込みシステム向けRTOSのシェアはTRON系が約60%

- インフィニオンのSiC-MOSFETは第2世代へ、質も量も圧倒

- 6Gに向けたサブテラヘルツ帯対応無線デバイス、100Gbpsの超高速伝送を実証

Agilexのロゴ 出典:インテル

Agilexのロゴ 出典:インテル IntelのPatrick Dorsey氏

IntelのPatrick Dorsey氏