Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く:Arm最新動向報告(6)(3/3 ページ)

「早く提供しないとRISC-Vにやられる」

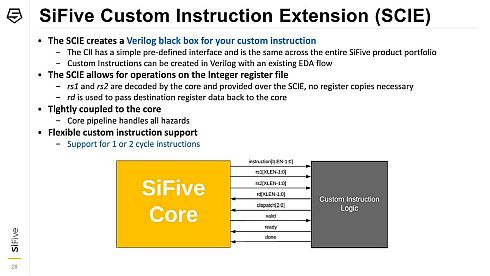

現時点では、Cortex-M33コアからCustom InstructionへのI/Fがどんなものか? といった情報はまだ無いのだが、概念的には図11みたいな形になるかと思う。

これはSiFiveのRISC-VベースのコアのCustom Instruction(SCIE)の構成だが、要するにコア部から命令とパラメータを渡し、結果を受け取るという仕組みである。SCIEの実装も、上で説明したCustom Instructionと似た条件(ただしレイテンシは2サイクルまでに制限されている)になっているし、さらに言えばMIPS ASEs(Application Specific Extensions)というカスタム命令拡張もほぼ同じである。要するに実装としてはごく当たり前ものになると思われる。

ところで冒頭の話に戻ると、なぜArmは今Custom Instructionの対応を行ったか。これについてはもちろんシガース氏とかは「ユーザーメリットにつながるから」という建前は崩さないが、エンセルグエイ氏との質疑応答の中で「早く提供しないとRISC-Vにやられちゃうから」という返事を頂いた。要するに、こちらの記事※)と同じ話である。

※)関連記事:ARMの“後払い”ライセンスに見え隠れするRISC-Vの興隆

RISC-Vと言っても実際は非常に多くのベンダーがそこに参画しており、当然IPの提供形態はまちまちであるが、RISC-Vの盟主といっても良いSiFiveは当初からサブスクリプションベースのライセンスを提供しており、Armの「Flexible Access License」はまさにこれに真っ向勝負を掛けている形になっている。そして今回のCustom Instructionも、RISC-Vが当初から用意していた(何しろ基本命令セットの中に、Custom Instruction用のフィールドが当初から用意されている)もので、Armに対するRISC-Vのメリットの1つとされていたものだ。

要するにRISC-Vとの徹底抗戦を最後までやり抜く、という強い意志の表れの1つが、Custom Instructionといえるだろう。

関連記事

- ≫連載「Arm最新動向報告」バックナンバー

加速するArmのプロセッサロードマップ、ソフトバンクによる買収が契機に

加速するArmのプロセッサロードマップ、ソフトバンクによる買収が契機に

2018年後半に入って急激に動きを活発化させているArm。本連載では同社の最新動向について報告する。第1回のテーマはプロセッサロードマップだ。 Armのサーバ向け戦略十年の計は実を結ぶか、新プロセッサ「Neoverse」

Armのサーバ向け戦略十年の計は実を結ぶか、新プロセッサ「Neoverse」

2018年後半に入って急激に動きを活発化させているArm。本連載では同社の最新動向について報告する。第2回のテーマはサーバ/クラウド向けの新たなブランド名として発表された「Neoverse」だ。 Armは自動運転向けプロセッサの覇権を握れるか、本命は5nmプロセス

Armは自動運転向けプロセッサの覇権を握れるか、本命は5nmプロセス

2018年後半に入って急激に動きを活発化させているArm。本連載では同社の最新動向について報告する。第3回のテーマは、「Arm TechCon 2018」でも地味ながらかなり力を入れていた自動車関連の取り組みを紹介する。 Armの組み込みLinux「Mbed Linux OS」が目指すセキュアな世界

Armの組み込みLinux「Mbed Linux OS」が目指すセキュアな世界

「Arm TechCon 2018」で発表された「Mbed」関連の最大のネタといえば、Armが提供する組み込みLinux「Mbed Linux OS」だろう。 ポスト「京」のプロセッサ「A64FX」はArmベースながら異彩放つ重厚系

ポスト「京」のプロセッサ「A64FX」はArmベースながら異彩放つ重厚系

「Arm TechCon 2018」では、Armのアーキテクチャライセンスを基に開発が進められている、次世代スーパーコンピュータのポスト「京」(Post-K)向けのプロセッサ「A64FX」に関する講演が行われた。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 5G通信の遅延時間1ms以下は複数端末の制御でも可能か、東芝が量子技術で道を開く

- CAN通信におけるデータ送信の仕組みとは?

- ソニーのLPWA「ELTRES」の通信モジュールが機能追加、システムの簡素化が可能に

- CANプロトコルを理解するための基礎知識

- イチから全部作ってみよう(7)正しい要求仕様書の第一歩となるヒアリングの手順

- 【問題7】10進数を2進数に変換するプログラム

- テスト消化曲線とバグ発生曲線の7パターン診断

- 組み込みシステム向けRTOSのシェアはTRON系が約60%

- インフィニオンのSiC-MOSFETは第2世代へ、質も量も圧倒

- 6Gに向けたサブテラヘルツ帯対応無線デバイス、100Gbpsの超高速伝送を実証