インテルの最新CPUアーキテクチャはより広く深く、GPUがHPCのムーンショットに:モノづくり最前線レポート(1/5 ページ)

インテル日本法人は、米国本社が2021年8月19日(現地時間)に開催したイベント「Intel Architecture Day 2021」で発表した、新たなCPUとGPUのアーキテクチャについて説明した。

インテル日本法人は2021年8月20日、オンラインで会見を開き、米国本社が同月19日(現地時間)に開催したイベント「Intel Architecture Day 2021」で発表した、新たなCPUとGPUのアーキテクチャについて説明した。

今回発表したのは、2021年秋の初めに市場投入が始まるクライアントPC向けCPU「Alder Lake」とデータセンター向けCPU「Sapphire Rapids」の基盤となるCPUアーキテクチャと、2019年11月に発表したGPUアーキテクチャ「Xe」を高性能ゲーミングやHPCに展開するための新たな技術である。

2025年に処理性能1000倍を実現するためのアーキテクチャ

インテル日本法人でCPUアーキテクチャの解説を担当したのは同社 執行役員常務 技術本部 本部長の土岐英秋氏である。土岐氏は「Intel Architecture Dayはこれで3回目となるが、今回の発表はこれまでよりはるかにもボリュームのある内容になった」と語る。

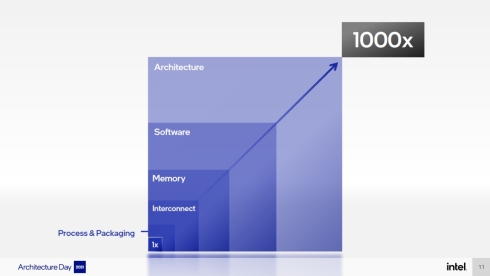

今回発表したCPUアーキテクチャ開発の背景にあるのが、顧客がコンピューティング処理に求める性能要求の高まりだ。最先端のユーザーは、現在の処理性能を1とした場合に、5年後の2025年に1000の処理性能を求めているというのである。「これは、2年で2倍の半導体の微細化を実現するというムーアの法則を越えている。半導体の微細化だけでなく、インターコネクト、メモリ、ソフトウェア、そしてアーキテクチャの進化を組み合わせることで成し遂げられるものだ」(土岐氏)という。

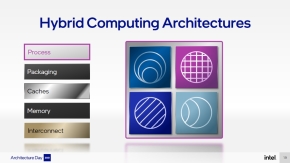

そこでインテルは、アーキテクチャ開発の方向性として、スカラー演算を行うCPU、ベクトル演算を行うGPU、行列演算を行うASICなどのアクセラレータ、データ伝送を担うFPGAなどのデータフローなどさまざまな要素を組み合わせた「ハイブリッドコンピューティングアーキテクチャ」を提唱している。さらに、ハイブリッドコンピューティングアーキテクチャに基づいて構成される半導体ダイをインターコネクト技術でつなげてワンパッケージにして提供する「ハイブリッドコンピュートクラスタ」として製品提供していく方針である。

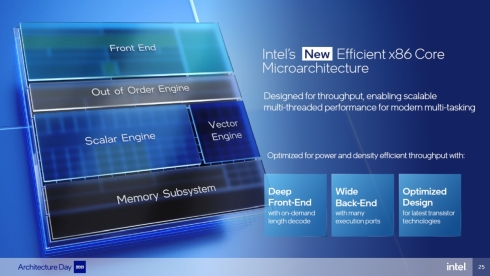

高効率の「Efficient Core」と高性能の「Performance Core」

こういった背景と“ハイブリッド”の方向性から導き出されたのが、高効率の「Efficient Core」と高性能の「Performance Core」という2つのx86アーキテクチャである。Efficient Core、Performance Coreとも、入力されたデータのデコードを担うフロントエンドを「Wider(より広く)」、デコード後の処理を行うバックエンドを「Deeper(より深く)」する方向性での性能強化が行われた。

Efficient Coreのフロントエンドでは、プログラムの分岐予測を精度よく行う「Accurate branch prediction」の機能を追加するとともに命令キャッシュを64KBに強化した。これらは、近年処理が求められるデータのサイズが大きくなっていることへの対応になる。デコード処理でも、3つのデコーダーから成るユニットを2セット用意し、1サイクルで6つの命令を読み込めるようにした。

デコード後のバックエンドのデータ処理では、処理ポート数を17とするなどして効率性の向上を図った。メモリサブシステムは、デュアルロード/デュアルストアでデータの出入り口を2つ持つようにし、L2キャッシュの4MBへの強化、データ処理のパイプラインを埋めて効率の良い処理が行えるようにバッファーも“Deep(深く)”になっている。そして、命令セットにセキュリティ関連に対応する機能を加えた。

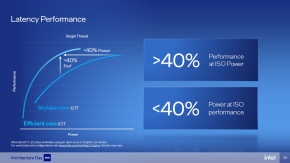

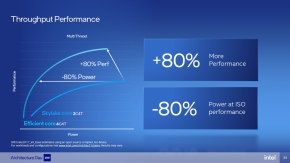

さまざまな機能強化が行われているEfficient Coreだが、消費電力の低減に向けて駆動電圧をできるだけ下げる方向性で設計されている。「Skylake」世代のCPUと比較すると、1コア1スレッドの場合に、同じ消費電力であれば40%以上の性能向上、同じ性能であれば消費電力が40%以下になる。また、4スレッド(Efficient Coreは4コア4スレッド、Skylakeは2コア4スレッド)の場合は、ピーク電力で80%の性能向上、同じ性能であれば消費電力を80%削減できるという。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 低価格FPGAでも文字認識AIの学習は可能なのか

- インフィニオンのSiC-MOSFETは第2世代へ、質も量も圧倒

- スバルが次世代「EyeSight」に採用、AMDの第2世代「Versal AI Edge」

- パナソニックの電動アシスト自転車にエッジAI機能を提供

- 自社開発のRISC-V CPUコアを搭載した32ビット汎用マイコン

- 東武ストアが指静脈による手ぶら決済を開始、酒類対応でセルフレジ利用率60%も

- CAN通信におけるデータ送信の仕組みとは?

- 過酷な資源ごみのビン色選別を自動化、PFUがイメージスキャナー技術から新規事業

- CANプロトコルを理解するための基礎知識

- 組み込みシステム向けRTOSのシェアはTRON系が約60%

インテル日本法人の土岐英秋氏

インテル日本法人の土岐英秋氏