PFNがGreen500で世界記録を達成した理由、独自発想のスパコン用プロセッサとは:人工知能ニュース(1/2 ページ)

Preferred Networks(PFN)は2020年11月16日、高い省電力性を特徴とする深層学習用スーパーコンピュータ(スパコン)「MN-3」の開発の意義や狙いを紹介する説明会を開催した。MN-3は同年6月22日に発表されたスパコンの省電力性能ランキング「Green500リスト」で世界1位を、同年11月17日に公表された最新のGreen500リストにおいては世界2位をそれぞれ獲得した。

Preferred Networks(プリファードネットワークス、以下PFN)は2020年11月16日、高い省電力性を特徴とする深層学習用スーパーコンピュータ(スパコン)「MN-3」の開発の意義や狙いを紹介する説明会を開催した。MN-3は同年6月22日に発表されたスパコンの省電力性能ランキング「Green500リスト」で世界記録を達成して1位を獲得している。また、同年11月17日に公表された最新のGreen500リストにおいても世界2位を獲得した。

スパコンにおける「省電力」の重要性

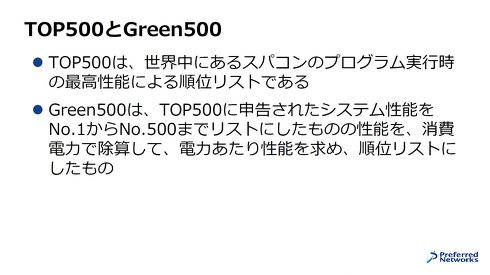

Green500はスパコンの省電力性能を指標として順位付けするランキングだ。スパコンの性能を比較する代表的な指標としては、この他に「LINPACK ベンチマーク」が存在する。スパコンで一次方程式の解を求め、それに要した総演算回数を計算時間で割り、算出された平均計算速度を指標として性能を比較する。Green500では、この平均計算速度をさらにスパコンの消費電力で割った値をベンチマークとして採用する。2020年6月に発表されたGreen500ではMN-3が世界1位を獲得した。

なお、平均計算速度を指標としたスパコンの性能ランキングである「TOP500リスト」においては、2020年6月に発表された第55回TOP500リストで、理化学研究所の開発したスパコン「富岳」が世界1位を獲得している。

PFN シニアリサーチャーの平木敬氏は、スパコンの性能指標として省電力に注目し、開発に注力する意義を次のように語った。「スパコンの計算処理性能を高める上で課題となっているものの1つが、スパコンセンターへの送電量だ。現在、スパコンセンターには最大で約30MWを供給可能だが、この送電量を劇的に改善することは難しく、せいぜい100MWが限界だ。1TWもの電力を送り込むことは困難だろう。このためスパコンの性能を向上させるには省電力化を目指していく必要があると考えている」(平木氏)。

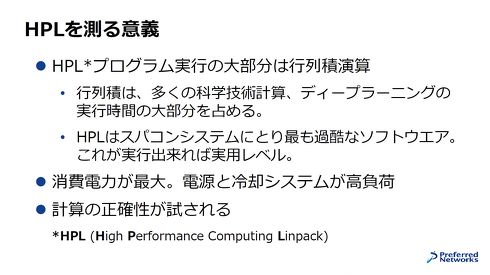

また平木氏は、LINPACKをスパコンの性能指標とすることに対して一定の議論があることにも触れる。「LINPACKを用いた性能比較では、行列積計算を中核とするHPL(High Perfomance Computing LINPACK)プログラムの処理能力を競う。過去にスパコンの応用分野として注目を浴びていた遺伝子解析などの分野では、行列積計算の重要性がさほど高くなかった。しかし、深層学習の分野では、その処理の大部分を行列積が占めており、その計算性能を測定することには意味がある。また、HPLは実行時に非常に多くの電力を消費するため、スパコンの電源と冷却システムが正常に稼働しているかを確認するのにも適している」(平木氏)。

「効率」を追求したプロセッサ「MN-Core」

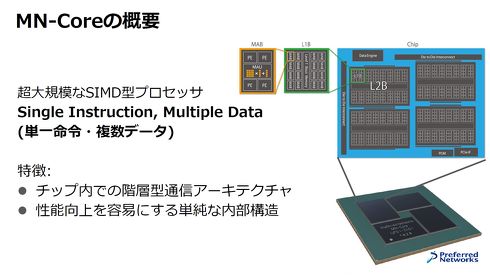

MN-3の大きな特徴の1つが、独自の設計思想に基づいて開発したプロセッサ「MN-Core」の存在である。MN-Coreは行列演算器(MAU)と4つのプロセッサエレメント(PE)を含むブロック(MAB)をチップ上で組み合わせた、階層型の通信アーキテクチャを特徴とするSIMD(Single Instruction, Multiple Data:単一命令・複数データ)型プロセッサだ。

MN-Coreの共同開発者である神戸大学大学院 理化学研究科 教授の牧野淳一郎氏は「MN-Coreは『原理的に可能な電力当たり性能を実現する』ことと『シリコン面積当たり性能でトップクラスを目指す』という2つの設計思想に基づいて開発した」と説明する。

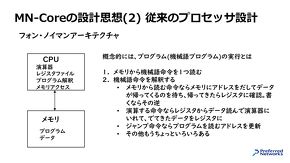

現在、コンピュータプロセッサのアーキテクチャ設計の主流は、いわゆる「フォン・ノイマン型アーキテクチャ」である。コンピュータ内部をCPUとメモリ部分に分けて、メモリから命令(プログラム)を1つずつ取り出して、CPUの演算機で解釈してから命令を実行していく。

このタイプのアーキテクチャは、CPUから送られてきた命令を1個ずつしか実行できない。その分、全体の計算処理にかかる速度は遅くなる。この課題を解決するため、これまで開発者は、コンピュータに搭載するCPUの数を増やす、CPUの演算コア数を増やす、複数の命令を実行できる仕組みや、命令が終わる前に次の命令を実行するパイプライン実行方式を導入するといったさまざまな工夫を重ねて、計算速度の向上を目指してきた。

しかし、牧野氏はこれらの工夫の結果として「ハードウェアの設計は非常に複雑、かつ大規模化してしまった。『計算を行う』という、ある意味で一番重要な役割を担うはずの演算機以外の回路がプロセッサの大半を占めることになった」と指摘する。加えて牧野氏は、通常のプロセッサ設計における「効率」の概念が「プロセッサが出せる最大処理能力の理論値に対する割合という意味でしかなく、設計したプロセッサ自体の電力効率が考えられていない」とも語った。

Copyright © ITmedia, Inc. All Rights Reserved.